Other Parts Discussed in Thread: TMS570LS3137, FDC2212

Dear TI team,

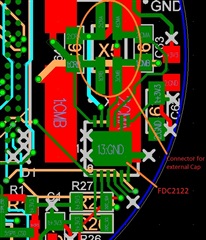

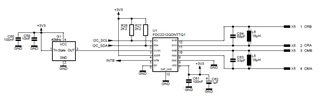

I am currently testing the FDC2212 on a self developed board with the TMS570LS3137 Hercules MCU. The circuit of the FDC2212 is shown in the picture below. For now the sensor is configured to only use one channel (Channel 0). The reference clock of 40MHz is divided by 2 by the setting of the corresponding register for Ch0. The Drive Current is set to be

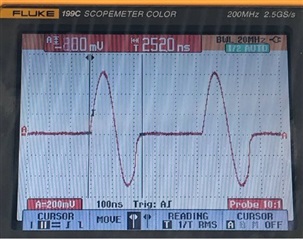

For testing the accuracy and feasibility for our application we have connected various capacities ranging from 10pF to 100pF. None of which we were able to measure correctly. So we captured the signal on port IN0A of the FDC which always looks like in the picture below with a peak voltage of about 0.6V. Which, according to the snoa950.pdf document, is too low. It should be at least double of what we measured.

Also the signal shape looks completly different of what can be found in the forum provided by other users.

Can you provide any guidance of where the problem could be located? Whether we have a wrong setup of the sensor or a problem in the hardware?

Many thanks in advance!