Hello All,

Connecting the AWR1243 to processor board.

Now AWR1243 is not giving any interrupt to processor board.

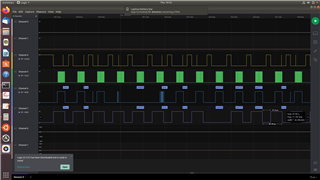

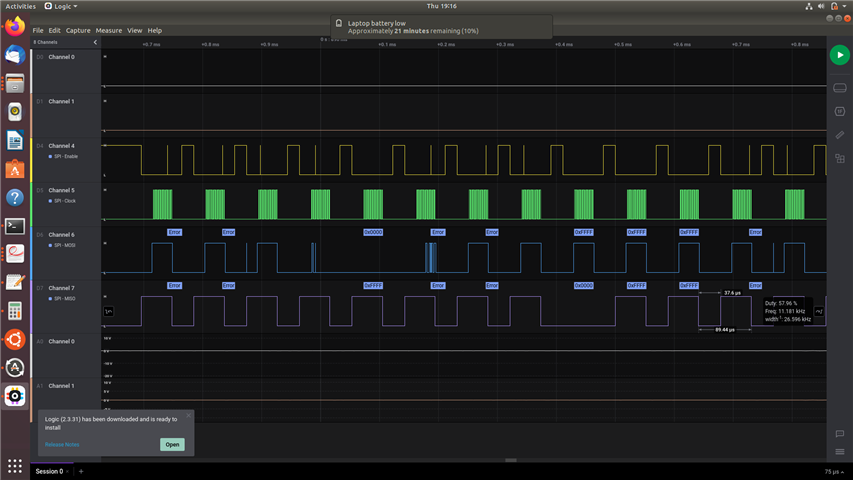

To check that what SPI command, it is receiving or What is happening inside the AWR1243 board,

need to enable the debug output on it.

Do we have any provisions to get the Debug output via serial cable or USB cable or JTAG cable?

We are using AWR1243 Booster EVM. From Host, SPI commands may be wrong due to wrong timing parameters.

-Thanks.