Hello,

When I debug the FDC2212, I found that the output has about 20mS delay which caused the level sensing is deeper. I only used Channel0, and configure it with single channel.

The register configuration is as following:

RCOUNT_CH0 2048

SETTLECOUNT_CH0 100

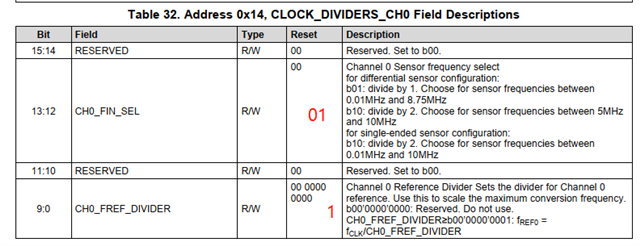

CLOCK_DIVIDERS_CH0 using external 40Mhz clock,0x2001

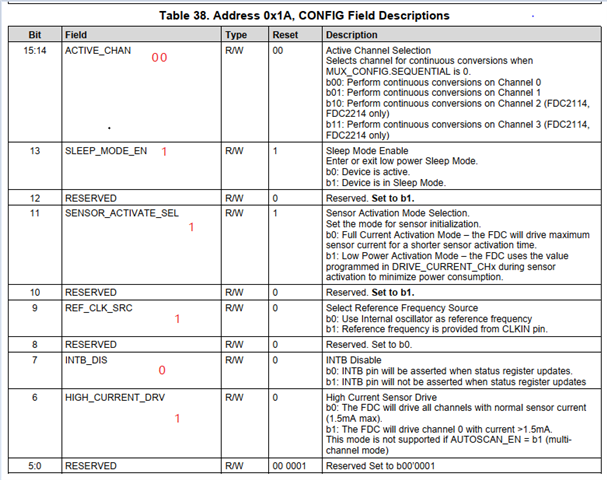

CONFIG

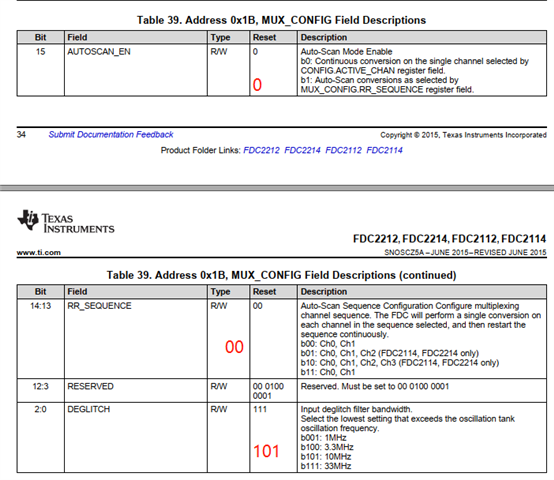

MUX_CONFIG

DRIVE_CURRENT_CH0 is decided when the Vpk is 1.7V and has been waked up ADC before conversion. In addition, I2C has no problem.

Could you please help to analyze?

Best regards

Kailyn