Other Parts Discussed in Thread: LDC3114-Q1, LDC3114,

Hello,

We use LDC1614 on our own board to detect the approach of metal on our coil.

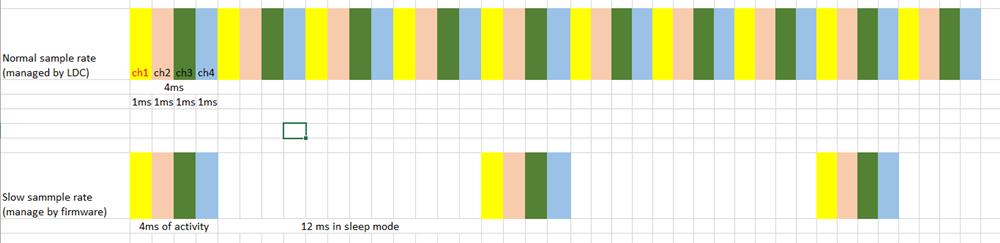

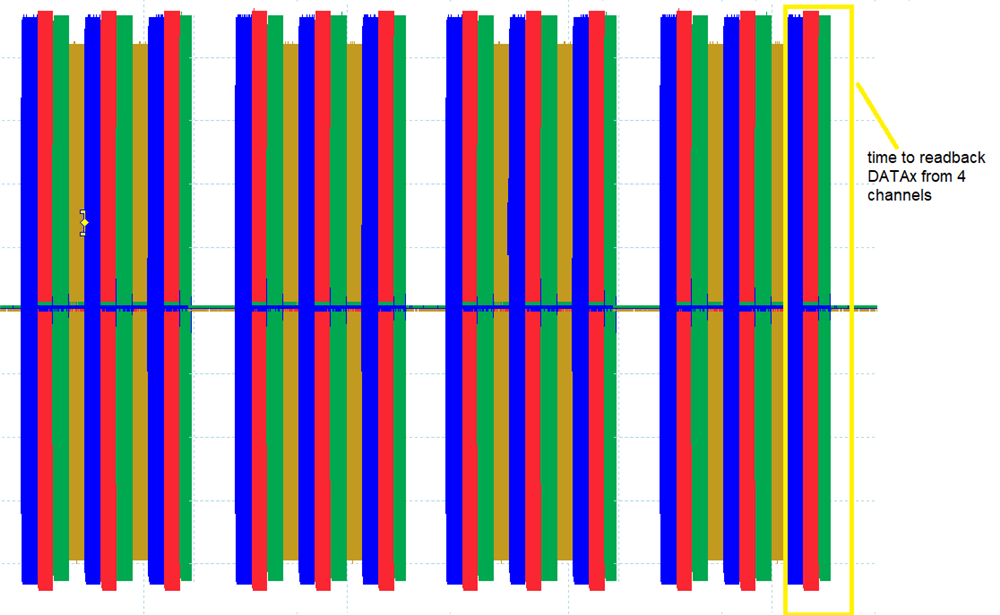

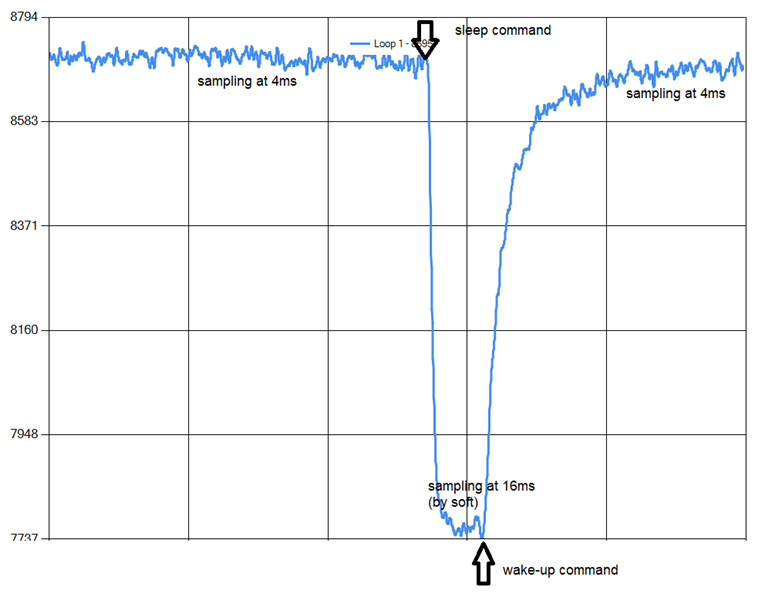

To optimize the energy consumption, we would like to slow down the sample rate (62.5sps) when there is nothing on the coil and increase it (250sps). We use multi-channel mode (4 channels).

To do this and to avoid changing too many registers' values, we manage it by software.

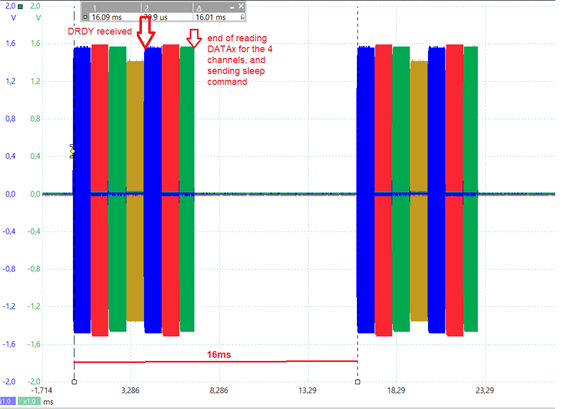

1. we use a timer with 16ms of the period to wake up the LDC1614

2. when DRDY occurs, we read data

3. put LDC1614 into sleep mode, and 16ms later the wake-up command will be executed

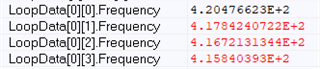

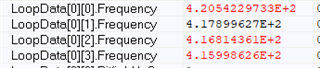

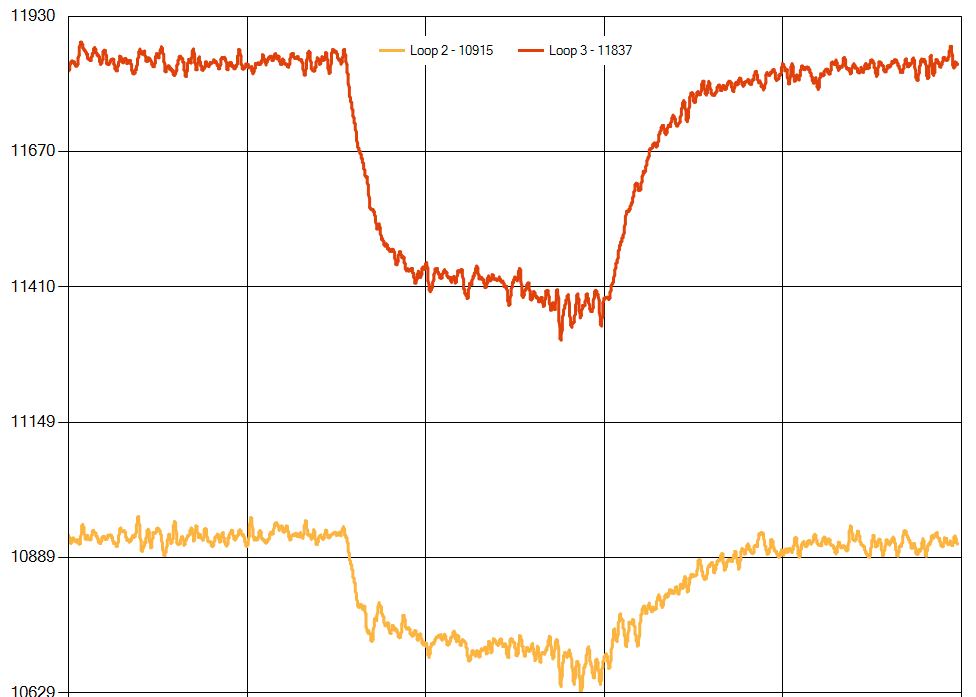

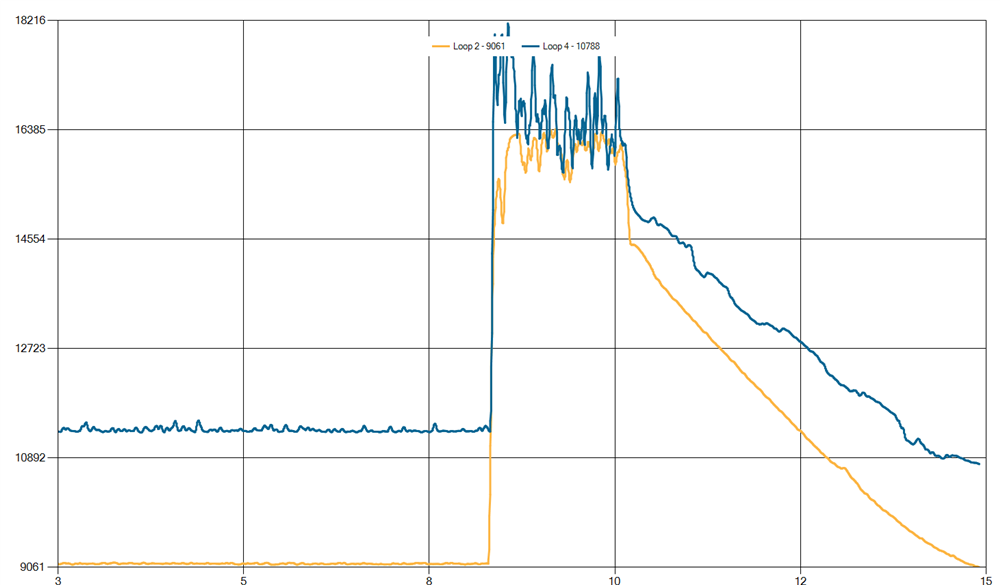

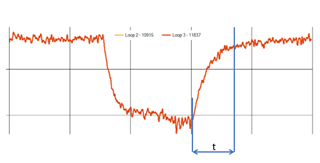

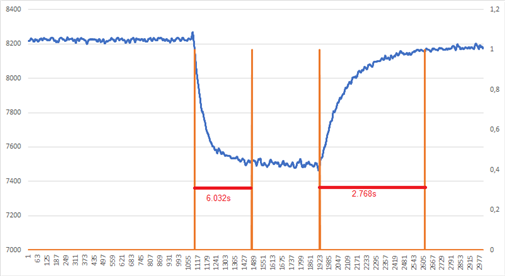

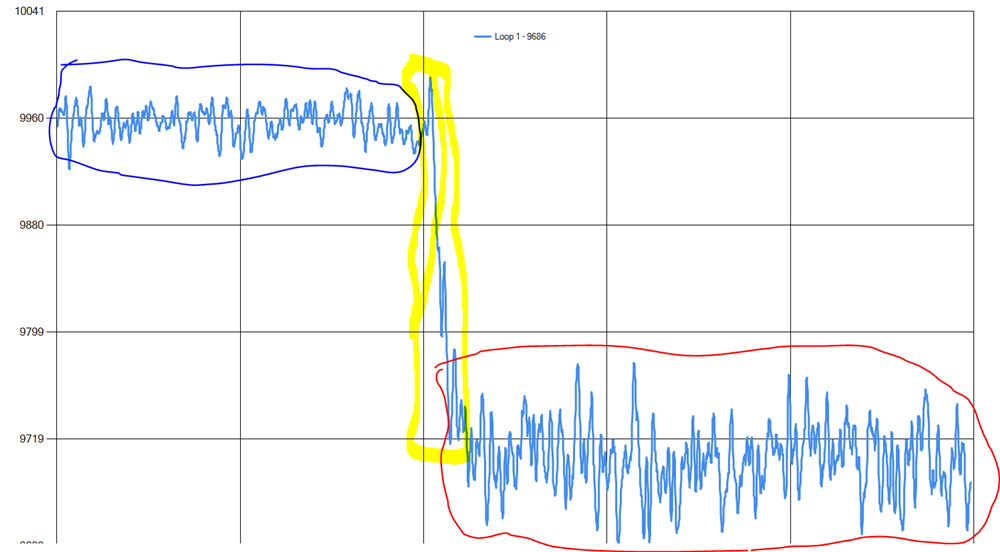

On the graph below, you have in Y-axis the value of DATA.

In blue, the part where the sample rate is high.

In red, the part where the sample rate was reduced.

In yellow, the transition where an offset appears. We changed nothing except the SLEEP-MODE_EN in CONFIG register.

Do you able to help us to understand how to manage this offset? Is it normal?

And when we speed up the sample rate, the offset appears but in opposite direction (offset is positive) and we arrived at the same amplitude of DATA before the sample rate was slow down.

The problem is, our analysis algorithm detects this amplitude changing as a new detection so some errors occur in our detection.

Thanks a lot for your help.

Kind regards