Hi.

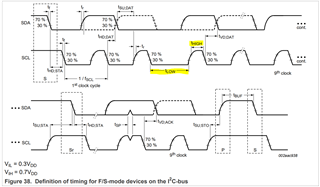

The I2C clock frequency is defined below in the AC characteristics of the TMP117 specifications.

Frequency: MAX400kHz

tLOW: Min 1300ns

tHIGH: Min 600ns

When CLK = 400kHz and Duty = 50%, both tLOW and tHIGH are 1250ns, which does not meet the above tLOW specifications.

In the specifications, Duty is about 1: 2, but in general-purpose microcomputers, Duty = 50% CLK is common and there is a contradiction in the specifications.

It works fine in terms of ability, but what should I think about this spec?