Hi,

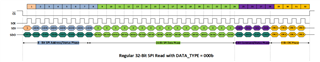

I am Trying to use the TMAG5170-Q1 Hall sensor with a Cypress Microcontroller, I am Facing a issue while reading the data across the SPI lines

Reading 84 0000 0E where E is the CRC calculated as per the datasheet. The data output expected is 00 7D83 00 but I am reading E0 0000 8B

Which I understand there is PRE_CRC_STAT, ALRT_STATUS1 and CFG_RESET bits set to high, As per the calculations and several debugging

I assume there is no error wrt CRC bits, Is there any key aspects that I am missing to employ or to lookout for ?

The CRC calculator that is being used here is as below:

char *MakeCRC(char *BitString)

{

static char Res[5]; // CRC Result

char CRC[4];

int i;

char DoInvert;

for (i=0; i<4; ++i) CRC[i] = 1; // Init before calculation

for (i=0; i<strlen(BitString); ++i)

{

DoInvert = ('1'==BitString[i]) ^ CRC[3]; // XOR required?

CRC[3] = CRC[2];

CRC[2] = CRC[1];

CRC[1] = CRC[0] ^ DoInvert;

CRC[0] = DoInvert;

}

for (i=0; i<4; ++i) Res[3-i] = CRC[i] ? '1' : '0'; // Convert binary to ASCII

Res[4] = 0; // Set string terminator

return(Res);

}

Please Guide me through this.