Hi Team,

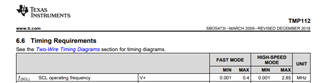

In TMP112 datasheet, it only has FAST MODE and HIGH-SPEED MODE timing requirements(no standard mode timing requirements).

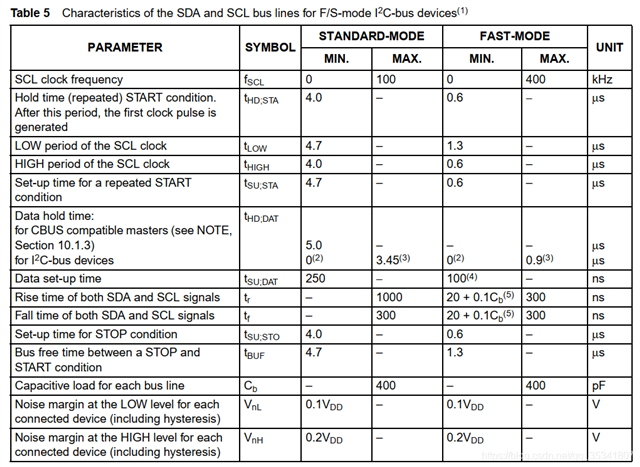

As I know, I2C runs as standard mode while clock frequency ≤100KHz. (Please correct me if I am wrong.)

Below is I2C standard-mode timing requirements of other TI parts I have read before.

Could you kindly confirm whether TMP112 is the same?

Thanks and regards.

Terry