Hi,

I tried to find out the frequency of VCLK peripheral clock to LIN module. I checked the TRM (SWRU599A) but I am confused with the info.

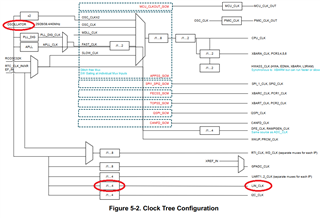

In below figure, it seems the LIN_CLK is from osc (40Mhz) and there is divider before the OSC to LINK_CLK. Where to set this divider?

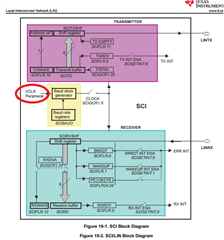

I also found below info in TRM. Is the VCLK same as the LIN_CLK in above figure 5-2?

I also found below info in LIN section of TRM.

At 100MHz peripheral clock, 3.125Mbits/s is the maximum baud rate achievable

Is the VCLK input to LIN mode in figure 19-1 is 100Mhz? If yes, how to get it with fiugre5-2? If not, would you pls tell me the right value of VCLK peripheral?

Thanks,

Chris