Other Parts Discussed in Thread: TMP102

Hi,

Please let me question at Two-Wire timing of TMP102-Q1.

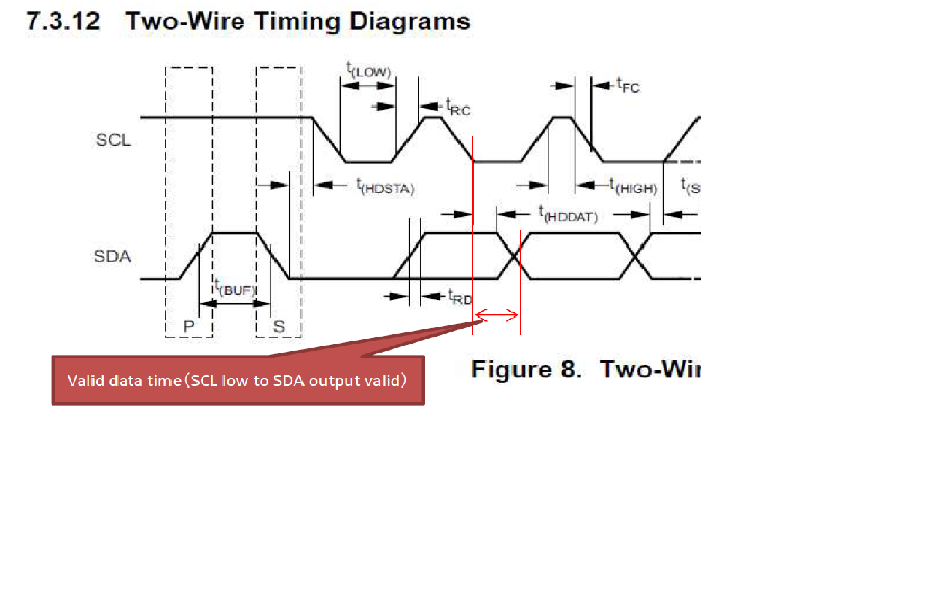

Data sheet for TMP102-Q1 (SBOS702C) page12 Two-Wire Timing Diagram is shown in Figure8.

I am at data timing, the time from when SCL goes low until SDA becomes valid I want to know.

However, it is not shown in Figure8.

Although it is a device, the I2C Interface Timing Requirements of PCA9524

"Tvd (data) Valid data time (SCL low to SDA output valid)" is regulated.

Please tvs of TMP102-Q1.

best regards