HI:

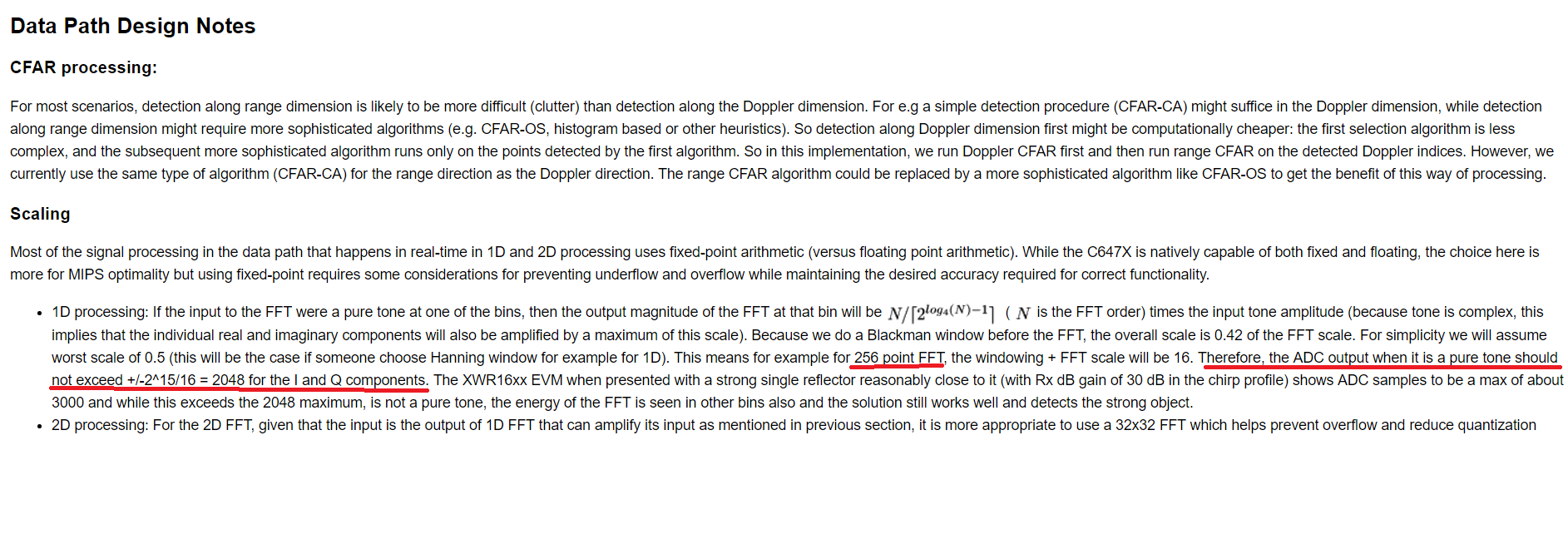

My question is about ADC out of AWR1642. Shown as follows, the doxygen indicates that the value of ADC outputs will not exceed +/-2048 to avoid overflow/nuderflow in 1D FFT (size of 256) outputs.

My questions:

- if the size of FFT is changed, is the full scale (FS) of ADC output also changed?

- Does the limitation of FS of ADC be mentioned in other document? I don't find the similar content in the datasheet and other training documents.

- what is the input range of ADC of AWR1642? I also don't find in the datasheet.

Thx

Stan