Other Parts Discussed in Thread: IWR1642

Tool/software: Code Composer Studio

Hello, TI engineers, I would like to ask a few questions:

1. How does IWR1642 allocate shared memory in L3? How to calculate the first address of shared memory, how is the memory size calculated?

2. How do I access the shared memory of the DSP in the ARM core (Cortex-R4F)? How to read shared memory data in ARM core (Cortex-R4F)?

3, I look at the register of 1642 found Cortex-R4F Memory Map

DSS_L3RAM 0x5100_0000 0x51FF_FFFF 2MB DSS_L3RAM (L3) shared memory space and DSP Subsystem Memory Map

DSS_L3RAM 0x2000_0000 0x201F_FFFF 2MB DSS_L3RAM (L3) What is the difference between shared memory space? Why is the memory address different? Is there two shared memory? The memory size is 2MB, but I looked at its data sheet to show a total of 1.5MB of memory, why is it bigger than 1.5MB here?

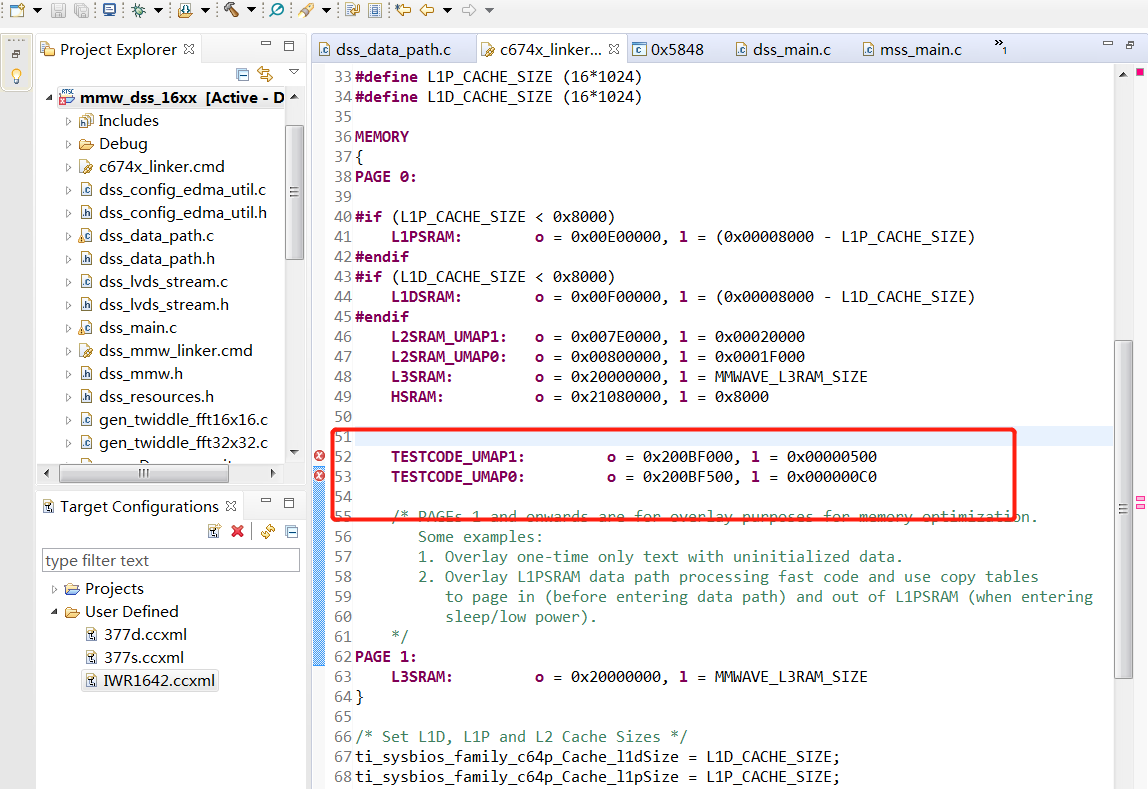

I now allocate 68KB as shared memory in L3 memory, but the program will report an error after compiling, saying that it is occupying L3 memory, but in fact, although this part of memory L3 is allocated, but the data in the memory is zero, I check The file found that L3 768kb is occupied, what should I do? Thank you.