Hi expert,

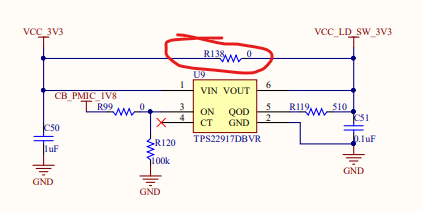

Customer made their own board followed our 6843ISK-ODS design. The power supply is 87702+5301. But sometimes 6843 could not power up correctly after power reset.

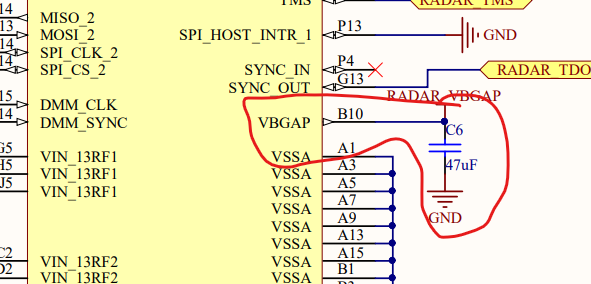

They measured 1.0V, 1.2V, 1.8V and 3.3V to 6843 when power up but didn't find problem. SOP is also set to 101 (3.3V) correctly.

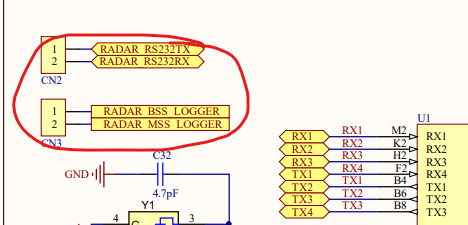

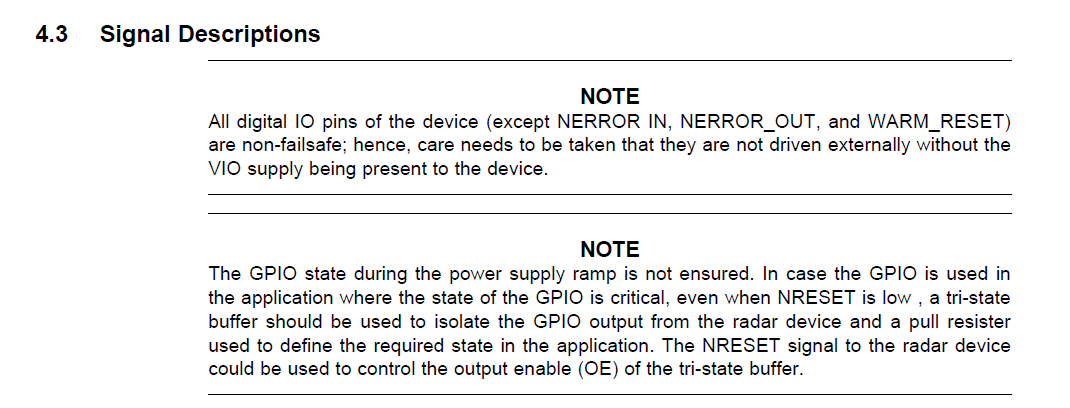

They could not get correct clock input from crystal, WARMRST is pull down for only 1~2us (not ~8us in crystal mode) and there is no output on 1V4_APLL.

I asked them to change external clock source and it still failed.

The PLL or oscillator may not be driven correctly inside 6843 but i checked their schematics and no problem was found.

Could you please give some suggestion to debug the board?

Thank you.

Regards,

Allen