Hi,

We had TDC7200 INTB questions to you?

We use 1.2K or 100K Hz LD trigger (STOP) to occue INTBs.

But TDC7200 got interupt INTB about 600 per second (0.6 KHz).

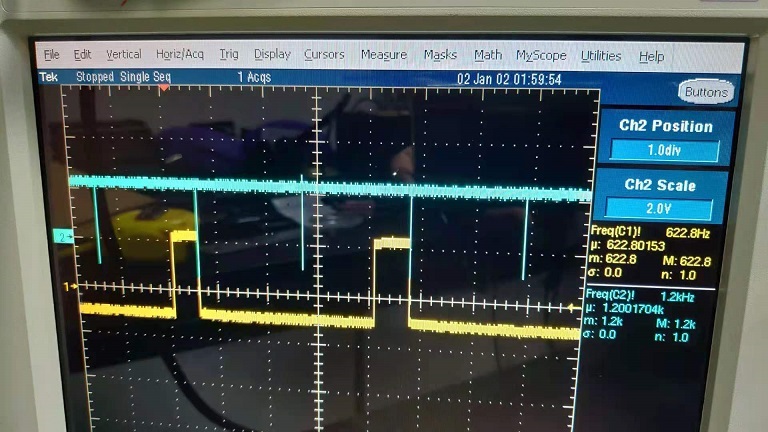

(Refer to P1_TDC7200.jpg, Yellow line is INTB and Blue line is STOP)

(1) Why we got one INTB every 2 Measurement Cycle when Measurement Cycle is set to 1 ? (Refer to P1_TDC7200.jpg)

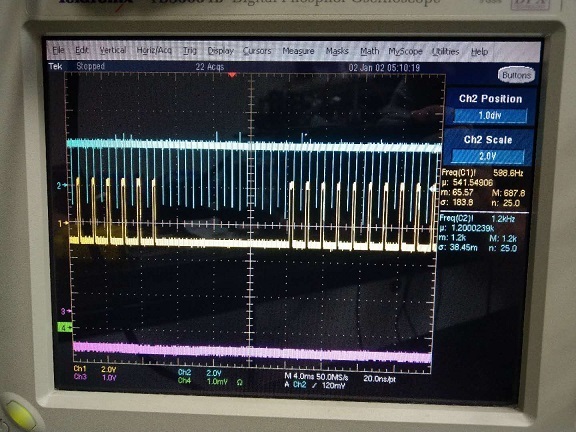

(2) Why we sometime got no INTB response after 17 STOP ? (Refer to P2_TDC7200.jpg)

(3) How to increase INTB to 100K ?

-----------------------------------------------------------------------------------------------------

Our FW settings as follows,

TI_TDC720x_SPIByteWriteReg(TI_TDC720x_CONFIG1_REG, 0x11, dev); // Default Mode 2

TI_TDC720x_SPIByteWriteReg(TI_TDC720x_CONFIG2_REG, 0x40, dev); // cal2 period = 10 clocks

TI_TDC720x_SPIByteWriteReg(TI_TDC720x_INTRPT_STATUS_REG, 0x0B, dev); // clear interrupt status

TI_TDC720x_SPIByteWriteReg(TI_TDC720x_INTRPT_MASK_REG, 0x07, dev); // interrupts enabled

TI_TDC720x_SPIByteWriteReg(TI_TDC720x_COARSE_COUNTER_OVH_REG, 0xFF, dev); // default

TI_TDC720x_SPIByteWriteReg(TI_TDC720x_COARSE_COUNTER_OVL_REG, 0xFF, dev); // default

TI_TDC720x_SPIByteWriteReg(TI_TDC720x_CLOCK_COUNTER_OVH_REG, 0xFF, dev); // default

TI_TDC720x_SPIByteWriteReg(TI_TDC720x_CLOCK_COUNTER_OVL_REG, 0xFF, dev); // default

TI_TDC720x_SPIByteWriteReg(TI_TDC720x_CLOCK_COUNTER_STOP_MASKH_REG, 0x00, dev); // default

TI_TDC720x_SPIByteWriteReg(TI_TDC720x_CLOCK_COUNTER_STOP_MASKL_REG, 0x00, dev); // default

P1_TDC7200.jpg :

P2_TDC7200.jpg :