We have a few concerns about Vdd=0v.

1. Vdd=0v, how about IO pin is Hi-Z or something

2. Vdd=0v, how about the logic pin

our application is SPI tree.

When the Vdd is no power supply, we need measure the IO is Hi-Z, not IO connect to gnd or Vcc.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

We have a few concerns about Vdd=0v.

1. Vdd=0v, how about IO pin is Hi-Z or something

2. Vdd=0v, how about the logic pin

our application is SPI tree.

When the Vdd is no power supply, we need measure the IO is Hi-Z, not IO connect to gnd or Vcc.

Hi Shih,

The TMUX1574 has both Powered Off Protection and Fail Safe Logic - these features will handle both scenarios that you are concerned with.

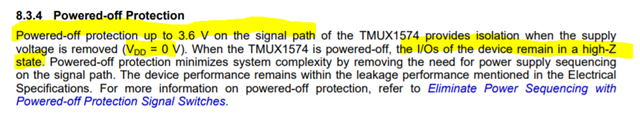

1 I/O pins are Hi-Z (with up to 3.6V protection on Analog I/O's when VDD = 0V). Please see the excerpt from the datasheet below:

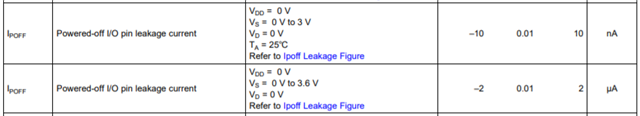

There is a small amount of leakage current that is possible - please see below for leakage under powered off conditions:

The first spec is 0V- 3V on the input at Room temperature and the second spec is from 0V - 3.6V on the input across temperature range (that is why there is an increase between the first and second spec)

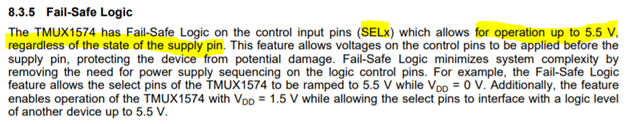

2. The input of the logic pin is high impedance normally due to digital logic gate architecture so the pin characteristics do not change much. However with Fail Safe logic up to 5.5V can be ramped up on the SEL pin while VDD = 0V without damage to the part. The device will not "switch" until VDD = 1.5V - please see below for an excerpt from the datasheet:

Overall the TMUX1574 should be able to work in this application without issue. This is a very popular part for SPI applications due to its configurations, channel specifications, as well as the protection features. All of these make the TMUX1574 an excellent choice for SPI applications.

If you have any other questions please let me know!

Best,

Parker Dodson