Other Parts Discussed in Thread: TS5A2053, HD3SS3411, TS3A5223

Hello,

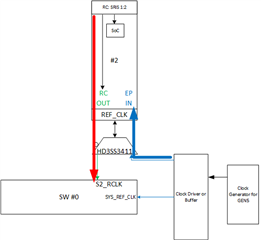

On my PCIE GEN5 Host design I need to support PCIE_REF_CLK (Connector pins A13/A14) to be an input or output from a SoC. The SoC pin is bidirectional.

The clock should support w/ or w/o SSC.

Could you please advise if the TS3A5018 will work for me?

Thanks in advanced'

Erez.