Other Parts Discussed in Thread: TMUX646, TS3A27518E

Hi there,

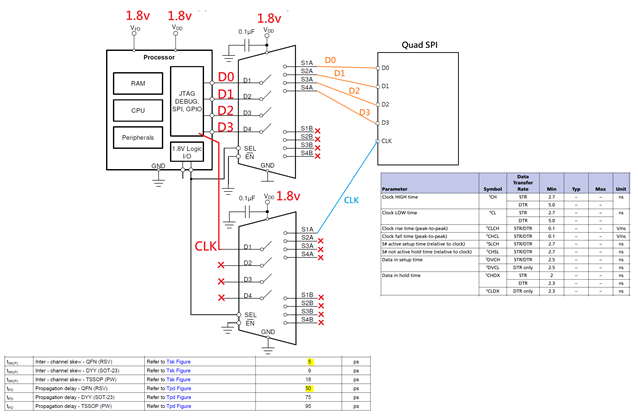

The picture below shows an application of the TMUX1574 for a Quad-SPI.

According to the datasheets of the MUX and the Quad-SPI, it seems 2 MUXs can work together.

Setup Time and Hold Time of the Quad-SPI are "ns" level.

The delays from MUXs are "ps" level.

We use one MUX for 4 Data, and the other for CLK only.

SEL pin is at a static level. (no change on SEL pin)

But somehow the design is not working currently.

May I know if this design makes sense from your experience?

Thank you so much for your replies in advance.