Other Parts Discussed in Thread: SN74CBTLV3126

Hi team,

do we have roadmap device support 3ch output to and spec be similar to TS3DS10224?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi team,

do we have roadmap device support 3ch output to and spec be similar to TS3DS10224?

Hey Dane,

We currently don't have anything on the roadmap but could you please expand more on what you mean by 3ch output? Can you maybe draw the expected function?

In most cases there is some creative way to create more niche mux functionality with multiple muxes. Would a solution like that be acceptable here or does it have to be a 1chip solution?

Thanks,

Rami

Hi Rami,

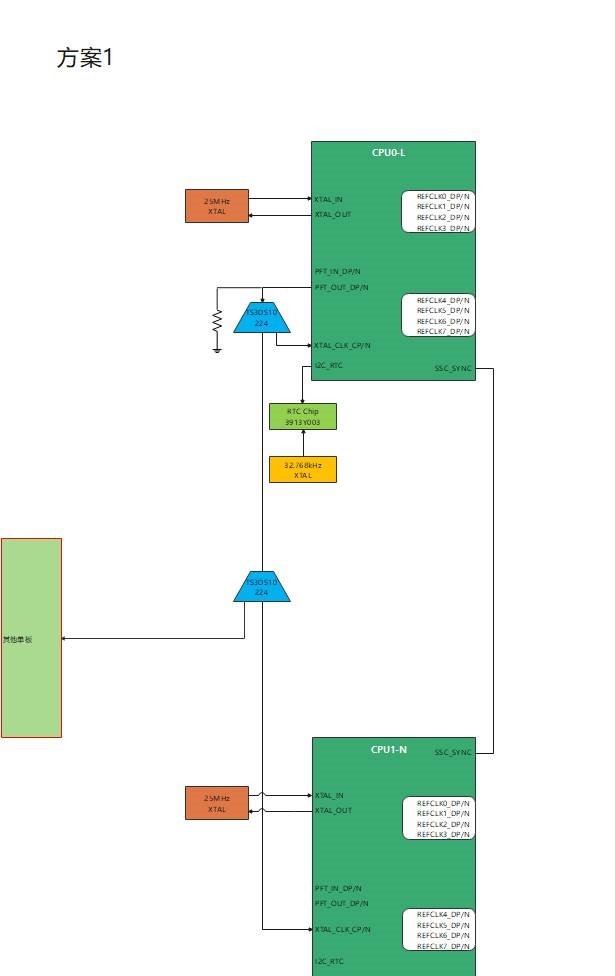

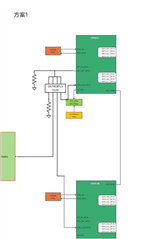

please refer to below application SCH. now we plan to use 2* 2ch to achieve the 3 output. but one problem is the latency/delay will be impacted if we use 2device solution. do you have some better idea?

Hi Rami,

add question:

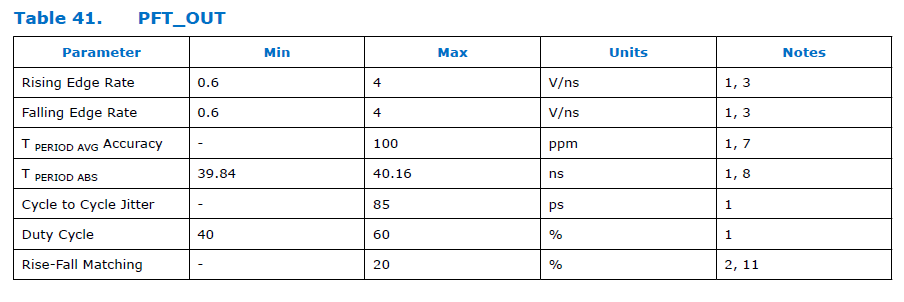

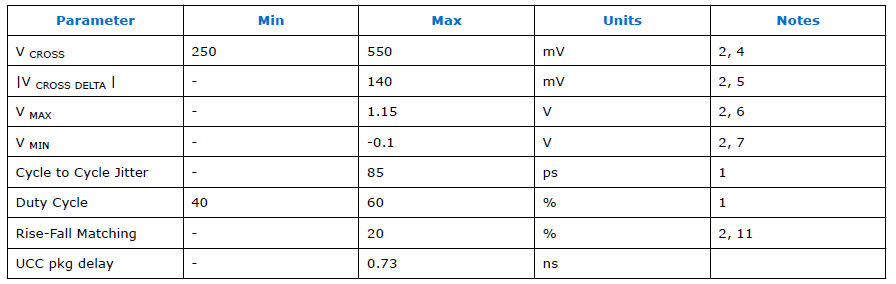

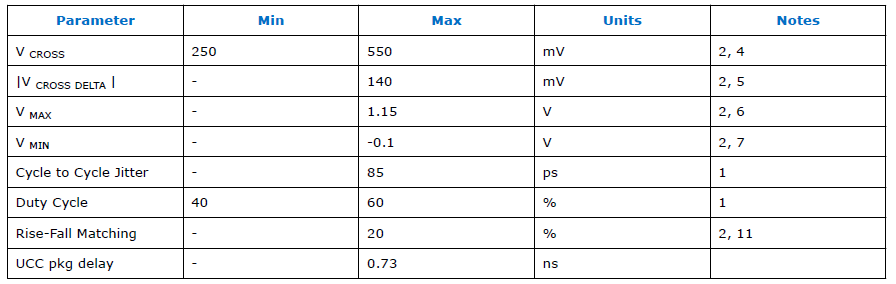

Is there a way to evaluate whether the signal output by PFTOUT-DP/N, after cascading through two stages of TSDS10224, can meet the requirements of XTAL-CLK-P/N?

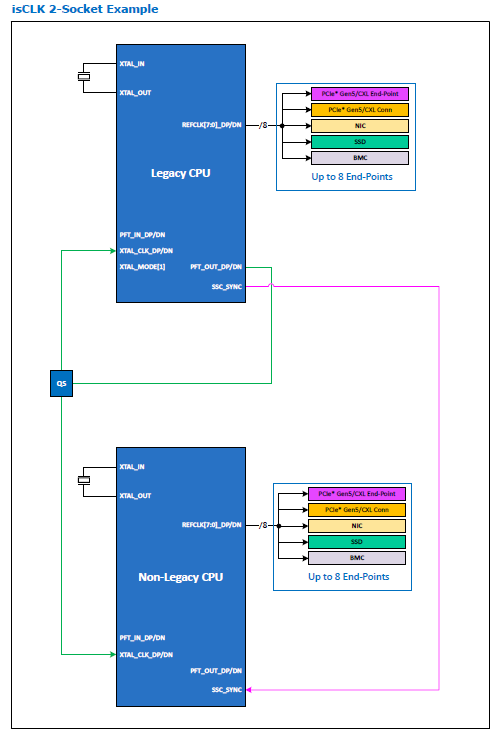

At present, the demo board of INTEL uses PFT.OUT-DP/N to send the clock to two CPUs through the first level TSDS10224. However, due to the need for an additional clock to be sent to other boards, it has been increased to two levels.

INTEL PDG solution as below:

Hey Dane,

I may be misunderstanding the use case here but is the idea to fan-out the PFT_OUT to three different locations?

Could a solution like this with the SN74CBTLV3126 work?

Here you would just feed the input into all 4 channels. The capacitance would increase a bit since it would technically be the same bus but if the period is only 40ns (25MHz) you should be fine with this implementation.

Let me know what you and the customer think.

If latency and delays are needing to be that precise between the three outputs then we certainly will want to reduce the use of cascading multiple multiplexers (see our app note here : Designing with Multiple Multiplexers in Series: A Guide to Cascading Multiplexers). Now we can select a mux with low and flat RON to help reduce the effects though but I think the above solution may be the best way to implement this.

Thanks!

Rami