Other Parts Discussed in Thread: OPA695

Tool/software:

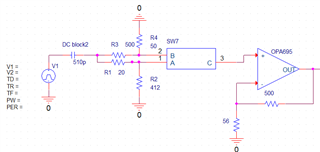

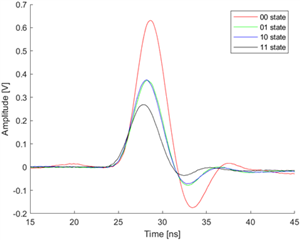

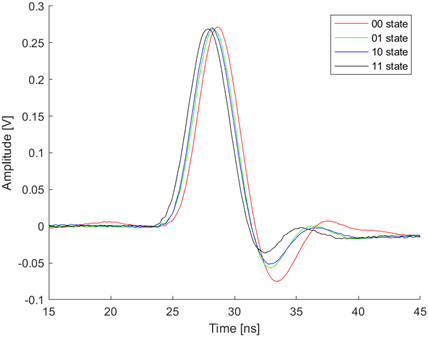

I design digital attenuator using SPDT. But this makes a signal delay by path. The graph below illustrates this delay. Both graph is OPA695 output signal. On the left, the signal is plotted as is, while on the right, the signal amplitude is normalized to the same level.

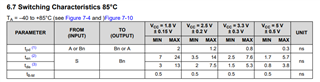

I need to understand why these delays occur. So I want to simulate the switch, but TI provides the IBIS model.

Can you explain how to model a switch using MOSFETs or BJTs?