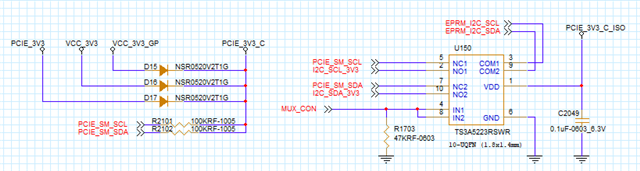

We're currently communicating with SMBUS and I2C via a MUX. Due to an I2C READ communication failure occurring through the MUX, we checked the MUX output and found that PIN 3 (CON1) SCL was not dropping low but was maintaining 2.9V. This appears to be the reason for the communication failure after 10 RETRY attempts.

The input PIN 2 (NO1) is dropping low (0V), and both the MUX's appearance and X-ray images confirmed no problems.

We checked the pin impedance of the MUX and found that PIN 8 (IN2) was 7.7 ohms. The PIN 1 (VDD) impedance was also 426 ohms.

However, when removing the MUX, the PIN 9 and PIN 10 pads fell off. This raises questions about the feasibility of the product's FA.