Hi Sir,

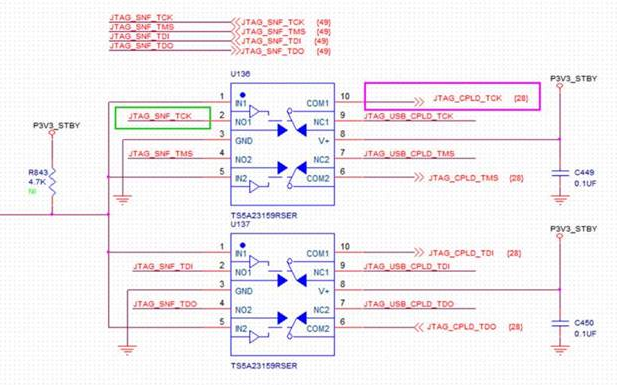

My customer design TS5A23159 as a JTAG switch as below.

The COM1 connect to CPLD JTAG CLK and NO1 connect to CPU JATG CLK.

And capture the waveform as below. We found the NO1 will have knee when voltage up to 2V as CH3(green) when working well.

Also found the COM1 waveform had claimed in 1.9V when the clock doesn't work.

Did you see this kind of phenomenon before? and any comments on it?

Please help on it, thank you.