Other Parts Discussed in Thread: TS5MP646

Hi Team,

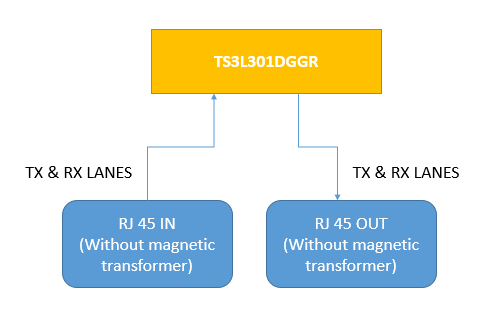

We are planning to use TS3L301DGGR part as analog switch in our project. We are just switching ON and OFF TX/RX lanes between RJ 45 IN and RJ 45 OUT using TS3L301DGGR as shown in below diagram.

Could you please help us what will be issues if we do not maintain control impedance in the PCB for TX and RX lanes of RJ45 since we are going with two layer PCB? Please let me know whether there will be any loss of data in the signal lanes? We are not using magnetic transformer between RJ 45 and analog switch.

It would be very helpful if you also let me know what will be current flowing in each lane of RJ45 (1000B-T) without magnetic transformer. I found that the ON-state switch current of is TS3L301DGGR +/- 128mA. Is TS3L301DGGR IC is advisable to use?

Regards,

Harshavardhan.K