Other Parts Discussed in Thread: TMUX1511

Hello,

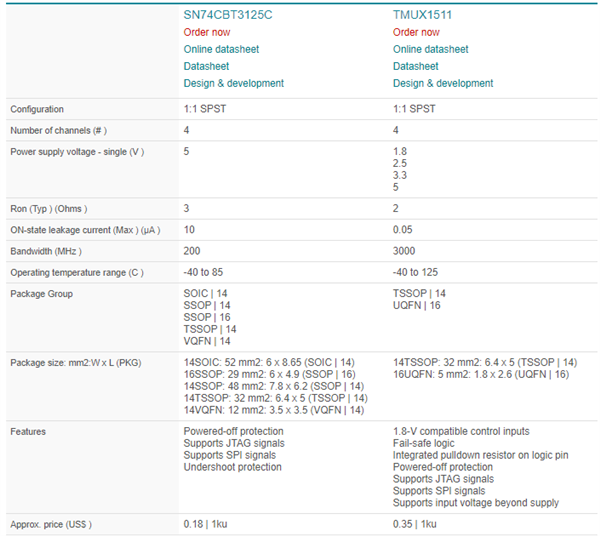

It seems I've made a mistake by powering the SN74CBT3125C with a 3.3V supply in my design. It's been working so far, but what operating parameters are limited at lower VDD?

The application is a 350kHz I2C bus for an external port.

- Ch 1: SDA

- Ch 2: SCL

- Ch 3: not used

- Ch 4: VCC to load device, <1mA

All signals are the same voltage as the SN74CBT3125C supply voltage (3.3V).

Thanks