Hi Team,

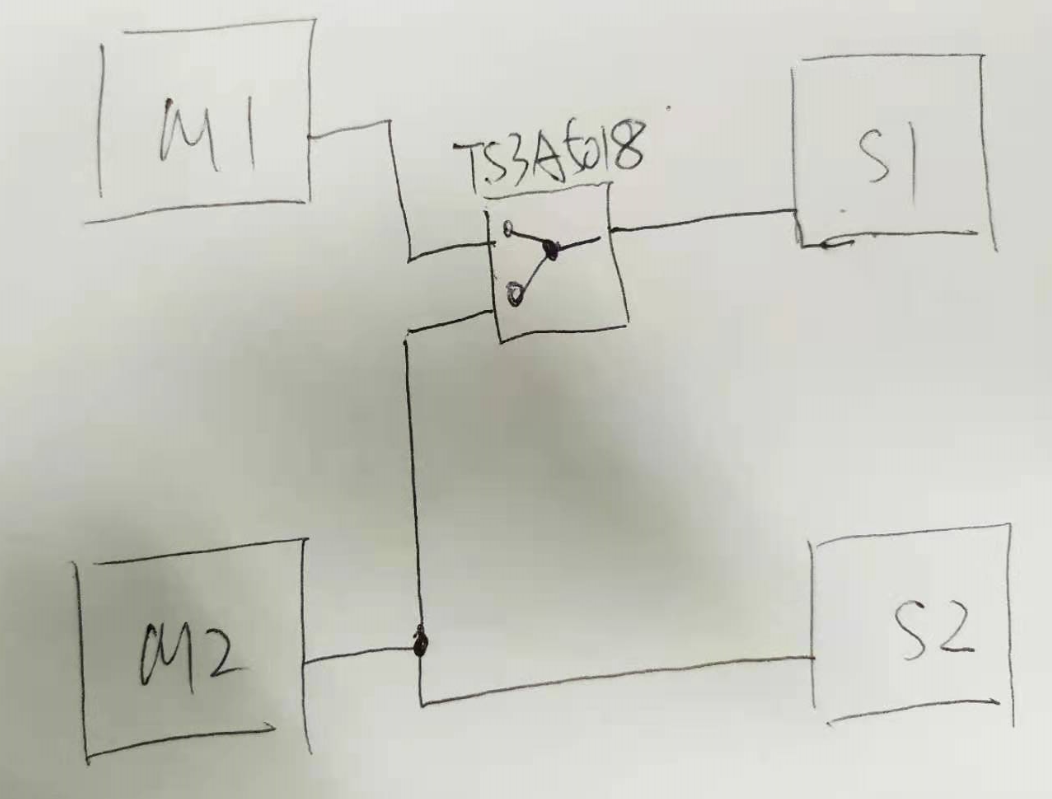

Whether "NC" pin can be used as "AND" logic with other signal at OFF state? The application is as the structure below: M1 and M2 are two different SPI masters. And M1 has two SPI slave devices S1 and S2. TS3A5018 is used as switch for S1 to connect with M1 or M2. I find in the datasheet, the INC leakage is <10uA at OFF state. Does "NC" is high-impedance state for OFF state? And the TS3A5018 could be implemented as the structure below? Thanks for your support.