Hello,

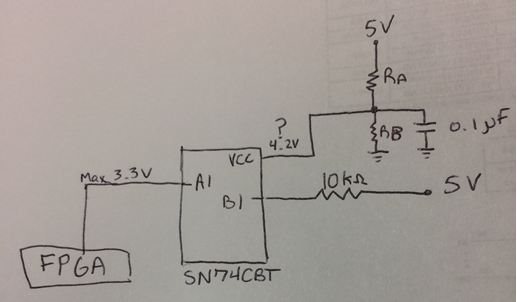

If we set VCC for all parts we buy to 4.2V, will this guarantee 3.3V max at the A side IO pins under all conditions? Wondering what the variation in VCC might be for each part we use to achieve the same 3.3V max on A side. +/- 0.2V, +/- 1V?

Thanks,

Nick