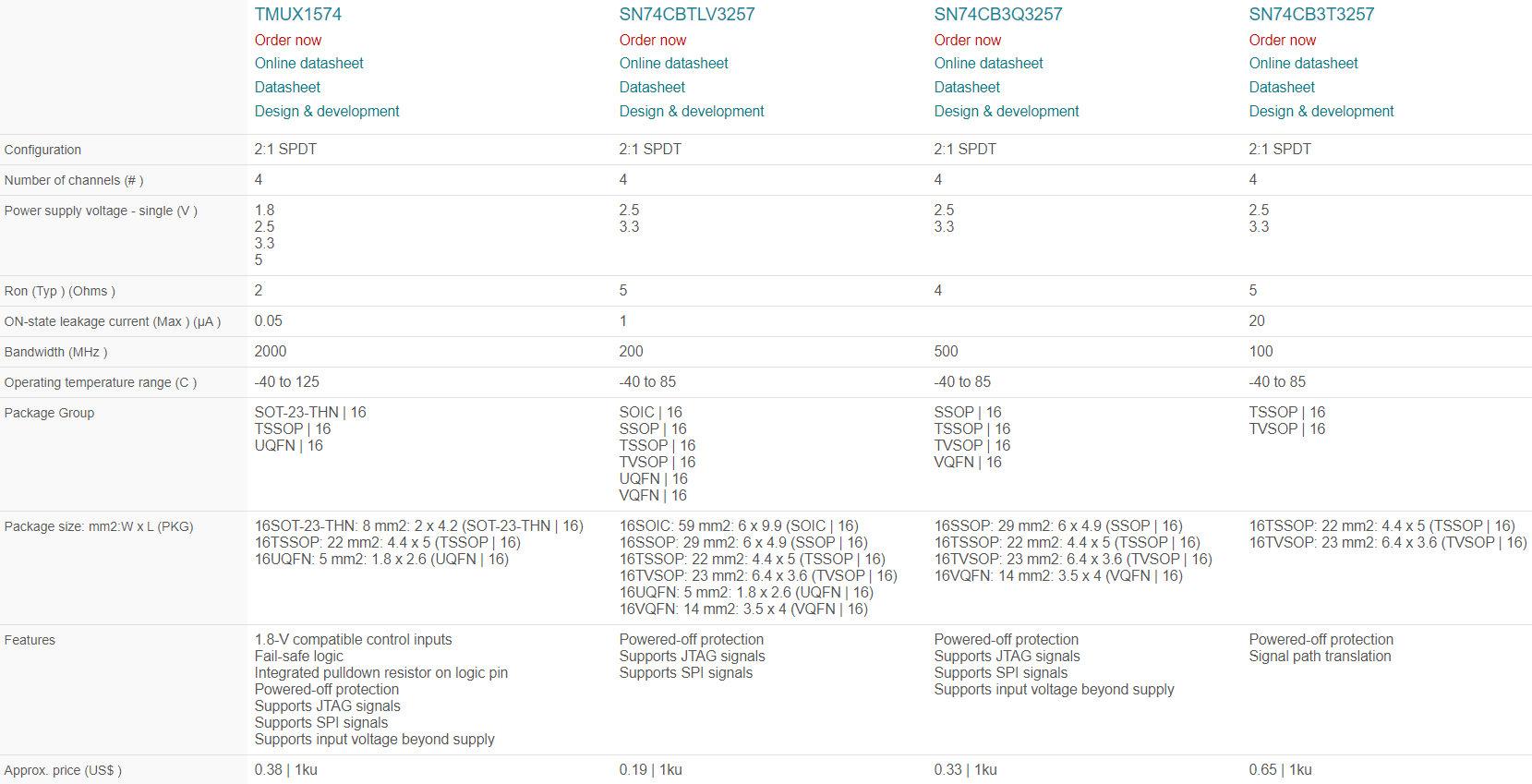

Other Parts Discussed in Thread: SN74CB3Q3257, SN74CB3T3257, SN74CBTLV3257

Hi Sir,

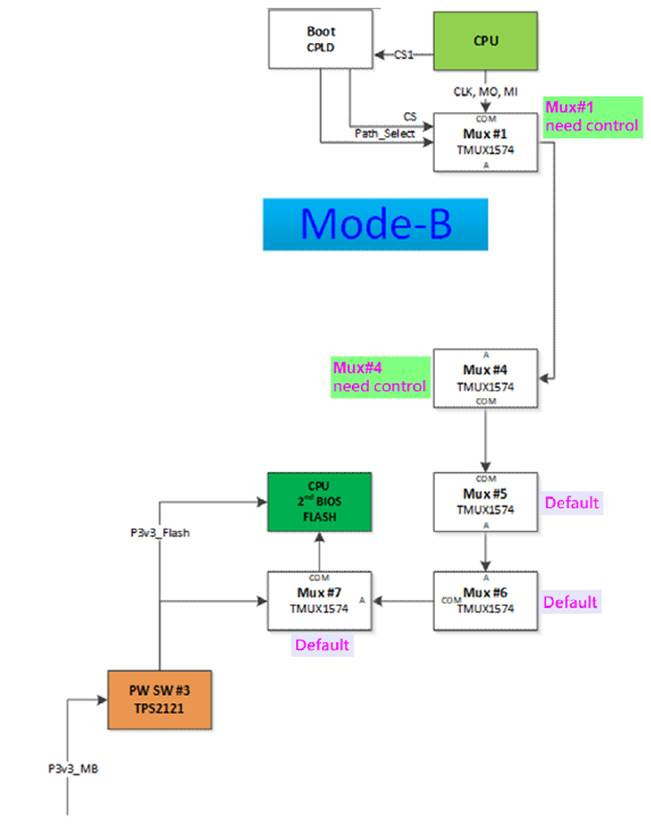

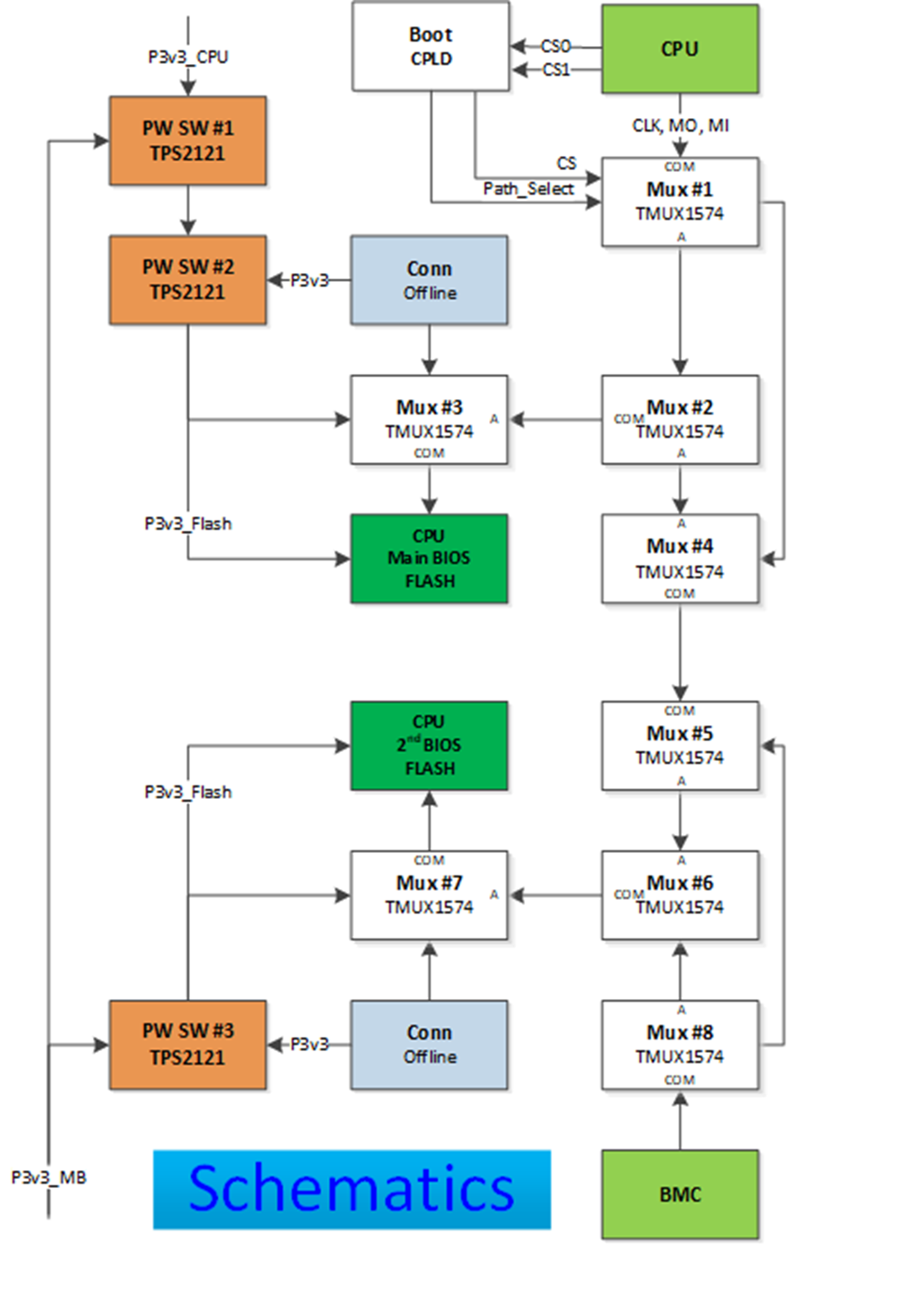

My customer is using 5 pcs TMUX1574 from CPU to SPI flash as below diagram,

And their SI team has concern about the signal integrity. So they have below questions and asking if there is any report or information on it.

Could you please help on it?

1. After switching, how long can I be sure the signal is stable? (SEL pin set to high from low, or reversed)

2. Does the ibis model (simulation model) provide unstable condition?

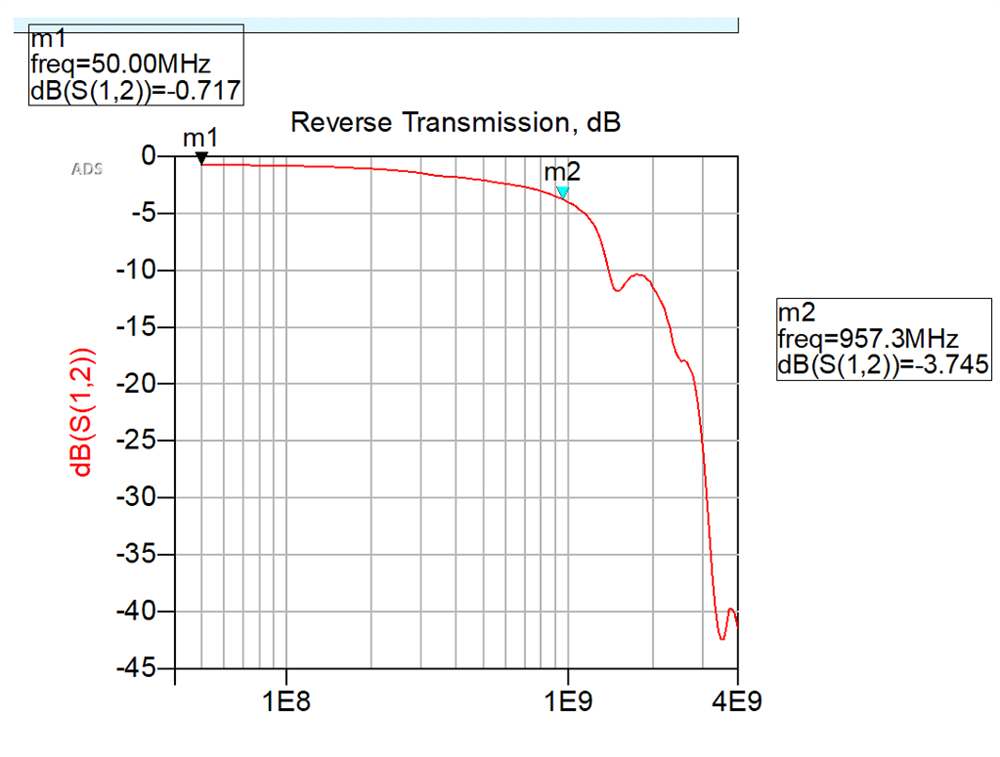

3. For SPI application, our SPI FLASH is operation on 50MHz with dual SPI.

4. Waveform amplitude @ 50MHz after 5 TMUX1574