Other Parts Discussed in Thread: TS3DV642, TS3USB3000

Hi Team,

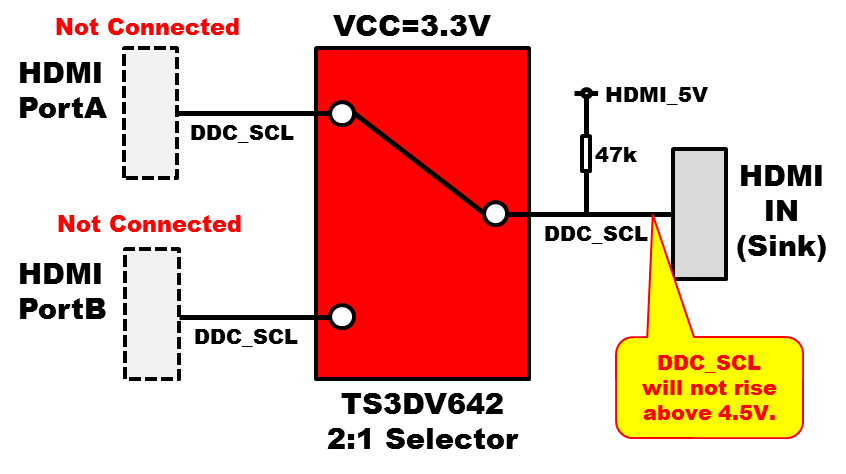

Our customer is using TS3DV642 as a 2:1 HDMI switch. Please see the set up below.

When they practiced HDMI compliance testing, DDC_SCL voltage were not able to keep over 4.5V when both HDMI port is OPEN.

If VCC of the device is increased up to 4.0V, DDC_SCL voltage met the HDMI spec.

[Q1]

Is there any restriction using TS3DV642 as 2:1 HDMI Input MUX to pass HDMI compliance testing ?

[Q2]

TS3DV642 recommended operating supply voltage is 2.6V to 4.5V. Does customer has any mistake using in below set up ?

[Q3]

Is there any relation between DDC_SCL output amplitude and VCC supply voltage ?

Best Regards,

Kawai