Hello Support,

I am using 4.9.7 version of ARM Compiler with TMS570LS3137 device [Cortex-R4 core]

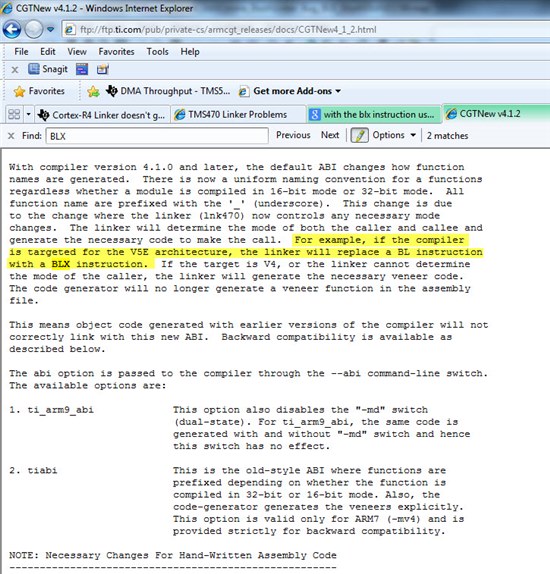

According to the page shown below, for Cortex-R4 ARM Compiler, whenever there is a function call from THUMB Mode to ARM Mode happens, Linker replaces the function call with BLX Instruction.

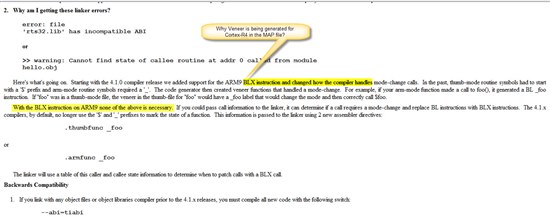

But in the attached ZIP file, if you see within Out folder's ECC99.map file, there is instead Veneer Section is generated.

Please let me know if it is a BUG in the Linker 4.9.7.

I have attached the Page from the following link with Markup for easy understanding.

In the ZIP file, once you unzip using FOLDER Option, you can run the compile_TI.bat file in order to rebuild the whole software provided you change the COMPILER Installation path within the BAT file according to your PC setup.

Let me know if you need any more information in order to debug this issue.

Thank you.

Regards

Pashan