Part Number: CCSTUDIO-KEYSTONE

Tool/software: Code Composer Studio

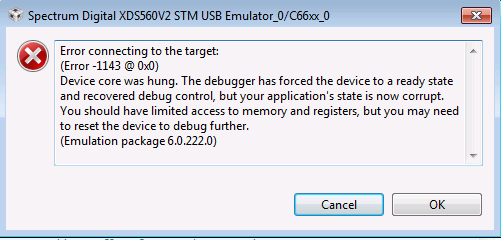

My project is using Keystone DSP 66AK2H06 and XDS560V2 USB emulator. When I do hardware reset, after Linux boot up, I load DSP in CCS window and click run, DSP runs OK. EDMA data transfer from FPGA to DSP L2 memory works good. But if I reload DSP in CCS window and click run, DSP runs but EMDA data transfer stops. Sometimes I got the following error message when I reload the DSP code. What do I missing in the code configuration?

Thanks

Mike