Tool/software: Code Composer Studio

We have a XDS560 PCI card running CCS4 under Windows 7 debugging a TMS320C6722B DSP processor.

It works but seems very slow. Loading a Program (~300KB takes about a minute). Single Stepping a line of C Code takes about 3 seconds.

We have have been doing this for several years on several computers (Windows 7 - 32bit) and using 2 different XDSS560 Emulators. This is the way we configure/program our motion controller boards we sell by the thousands. Strangely one configuration would load a Program in ~ 1 second where the other would take ~1 minute. We weren't able to determine why. At one point we assumed it was related to the particular XDS560 but swapping them didn't swap the speed issue. We no longer have the "fast" computer or configuration. Everything we try works but is slow.

Can anyone give any hint to why sometimes it is fast and sometimes orders of magnitude slower?

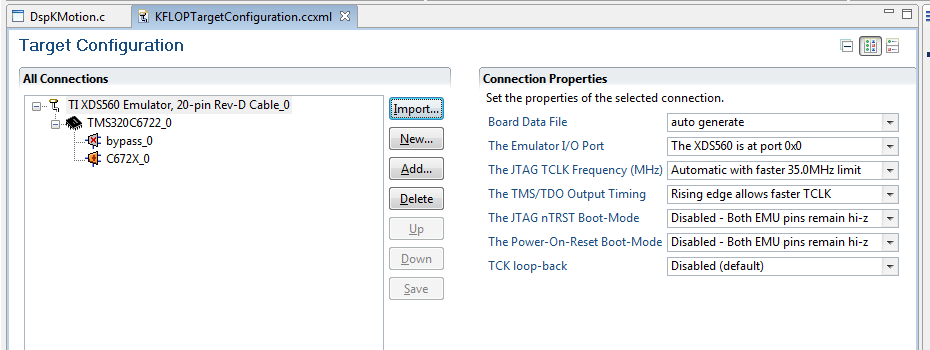

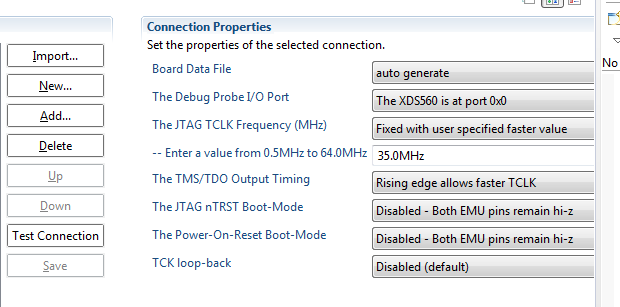

Under CCS4 | Target Configuration | TI XDS560 | JTAG Frequency we've tried most of the options with no change of the speed