Other Parts Discussed in Thread: TPS65023

Hi Team,

I have a customer with some questions about the TIDA-01480

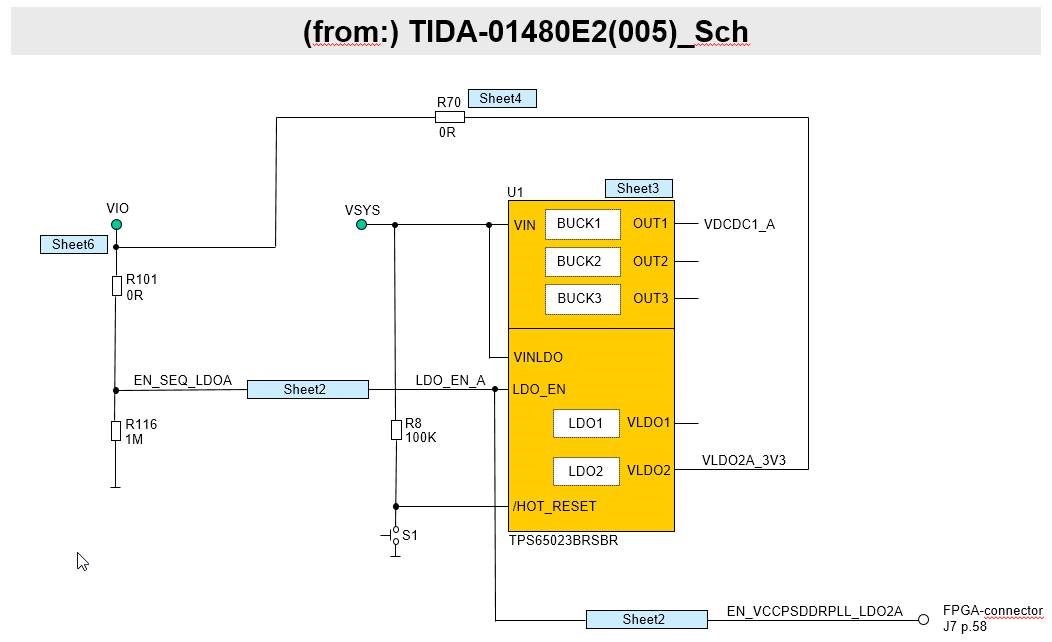

I cannot understand how exactly the circuit starts. I have prepared a diagram of the TIDA again (so this is an exact equivalent from TIDA-01480):

VIO is the most important voltage when starting, as this voltage is used to generate the power sequencings. At the same time, this voltage is controlled via the seq signal EN_SEQ_LDOA - or initially blocked!?

I don't understand this loop - the output of LDO2 is directly connected to its own enable input. (Sheet2 are pure wire connections) The reset button S1 could still play a role, but according to data sheet TPS65023 it only affects the VDCDC1 output. An important question is whether the TIDA-1480 board starts at J7 without an FPGA board docked?

Regards

Mihir