Other Parts Discussed in Thread: BQ78350-R1, BQ78350

Hi all,

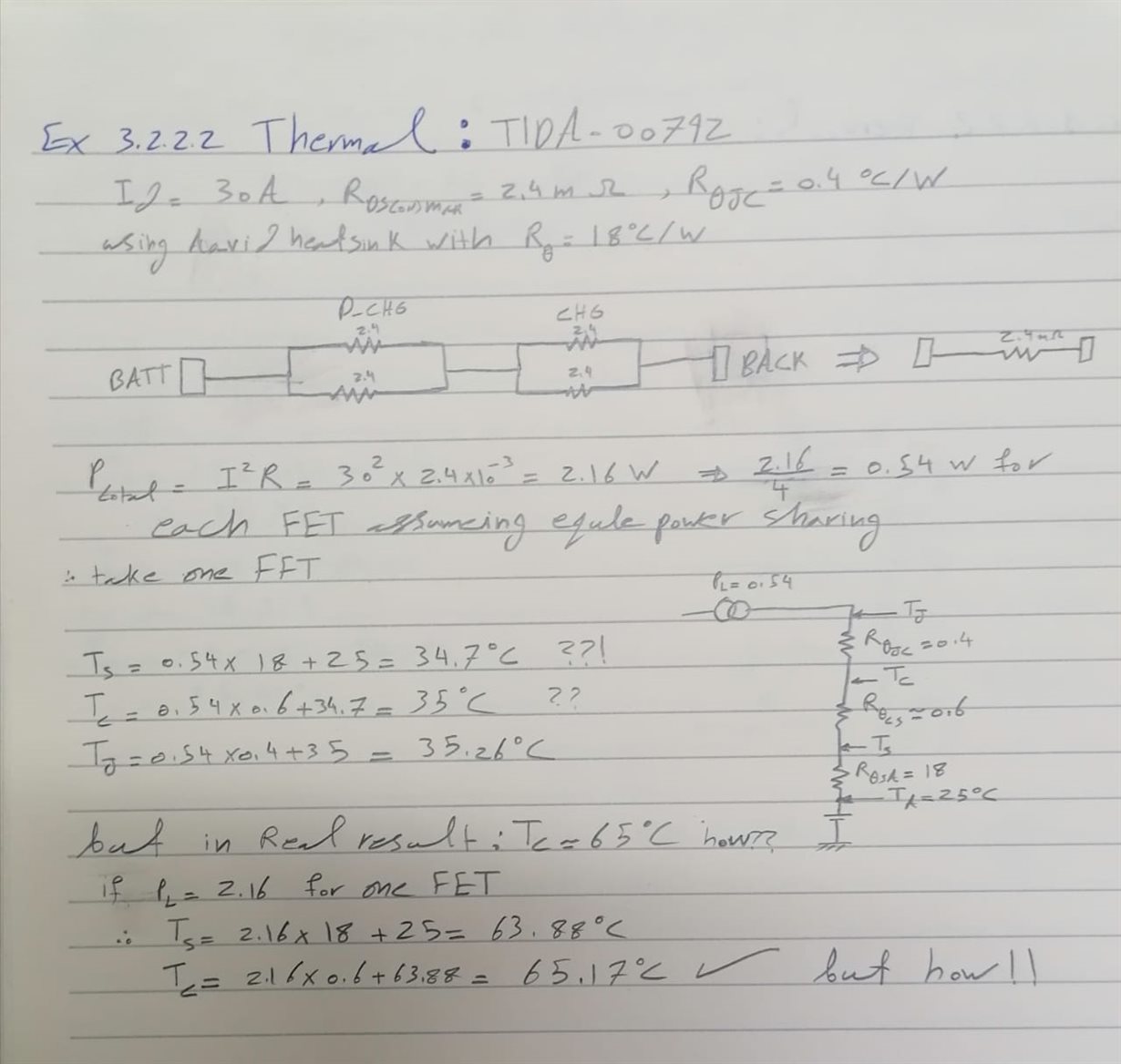

I just design a new BMS based on many reference designs with my own requirements, considering TIDA-00792 in "3.2.2.2 Thermal" when making the calculations based on total P_losses = 2.12W but with one FET everything goes right but as I think every MOSFET will share P = 0.54W (assuming equal power-sharing) so calculating based on P= 0.54W the result is far away from real value! why?

another question in my design the 4 FET share the same heat sink and total P_losses = 24W, it's correct to parallel the Junction-to-case thermal resistance, right?

the same heat sink and total P_losses = 24W, it's correct to parallel the Junction-to-case thermal resistance, right?