Hi team,

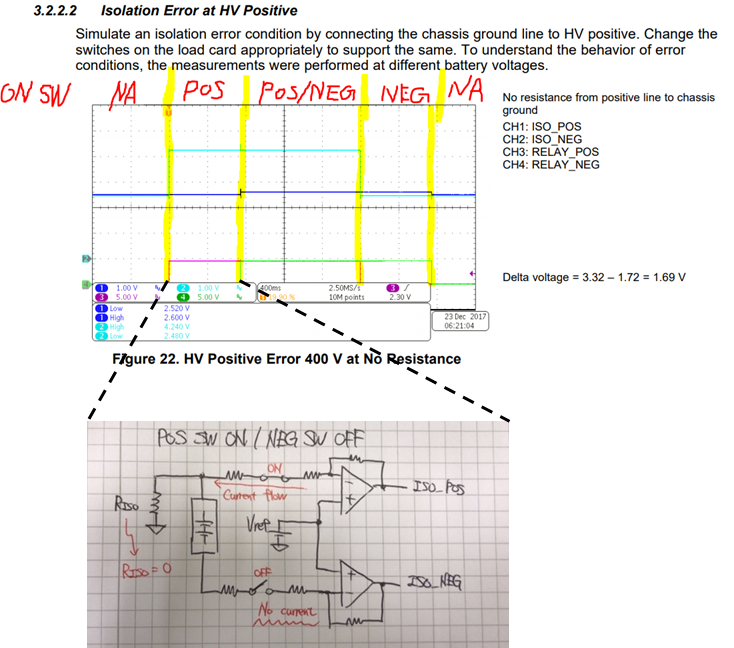

Could you tell me why ISO_NEG goes high while only POS_SW is on-state with HV positive error test?

I referred to figure.22. I thought ISO_NEG would keep Vref because there is no current path via lower side resistors but it didn't. Could you show me the current path in that state and equation about ISO_NEG in this state?

Or did I misunderstand the switching state?

Best regards,

Ochi