Other Parts Discussed in Thread: TINA-TI

Tool/software: WEBENCH® Design Tools

Hello there!

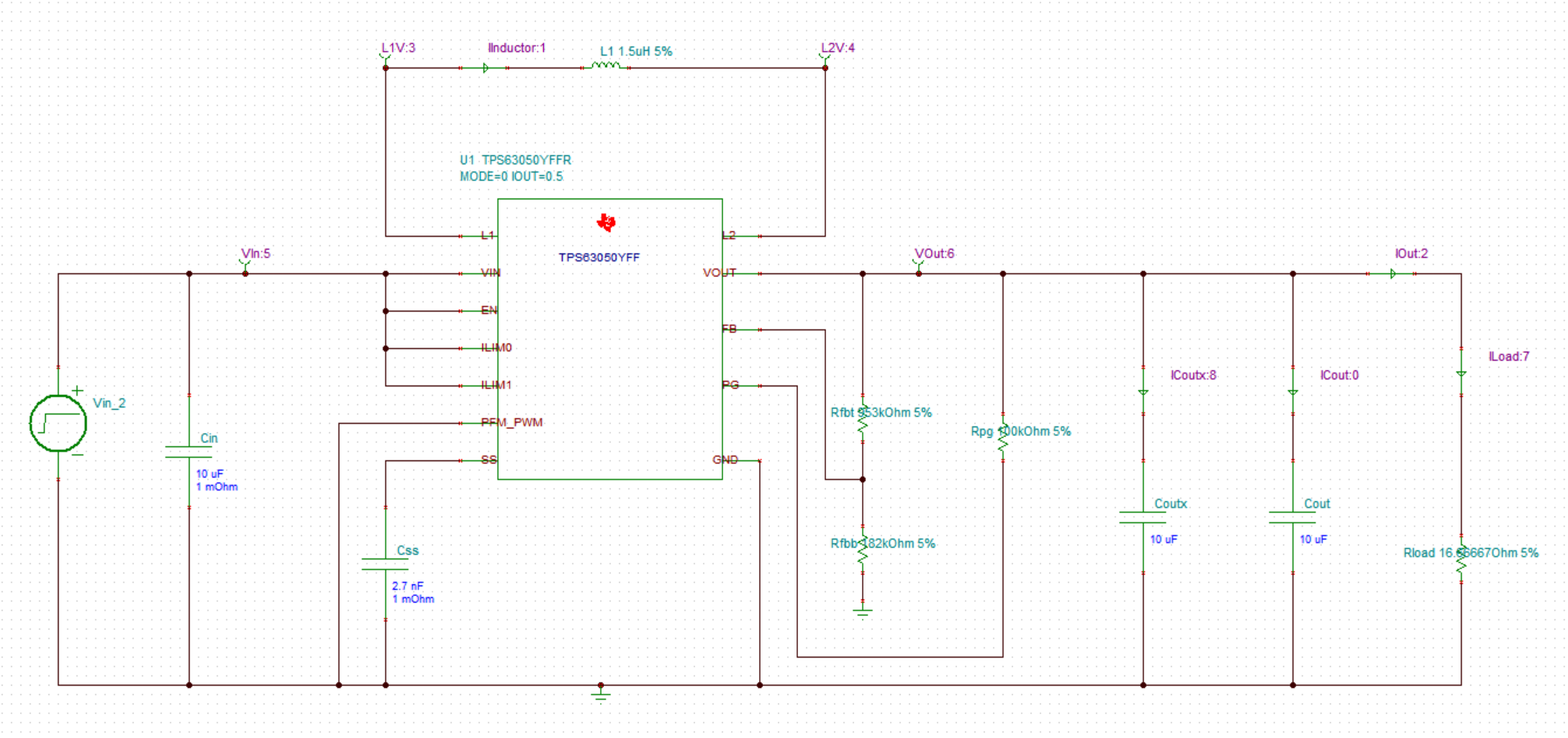

I designed a boost converter using TPS63050 on the WEBENCH Power Designer for generating a 5V/0.5A supply from a single-cell Li-Ion/Li-Po battery. The WEBENCH Power Designer completed the recommended circuitry as well as provided suggestions based on the specifications I provided. And that's a really nice thing about it. However, there seems to be a little catch in this.

The circuit is as follows:

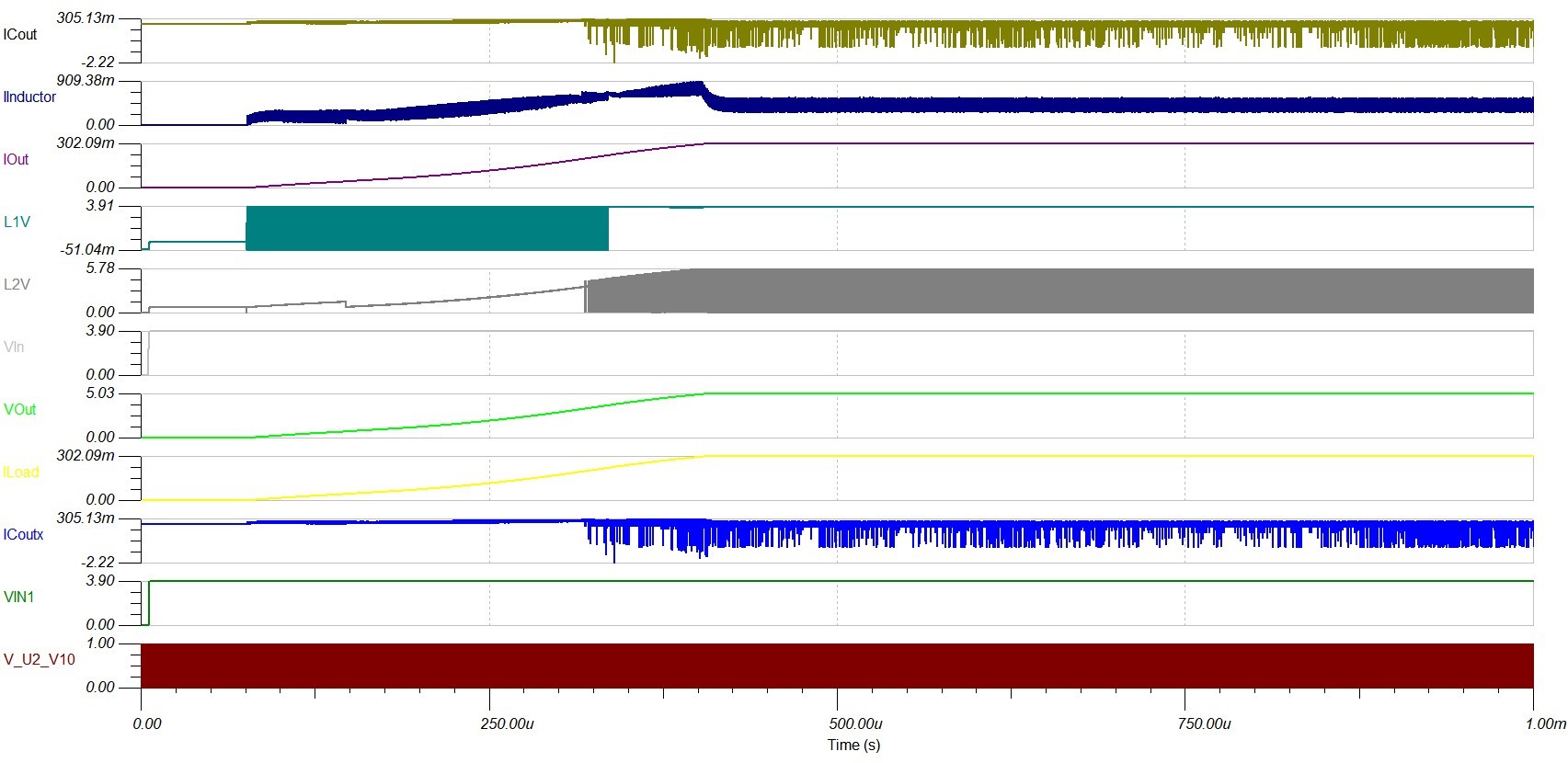

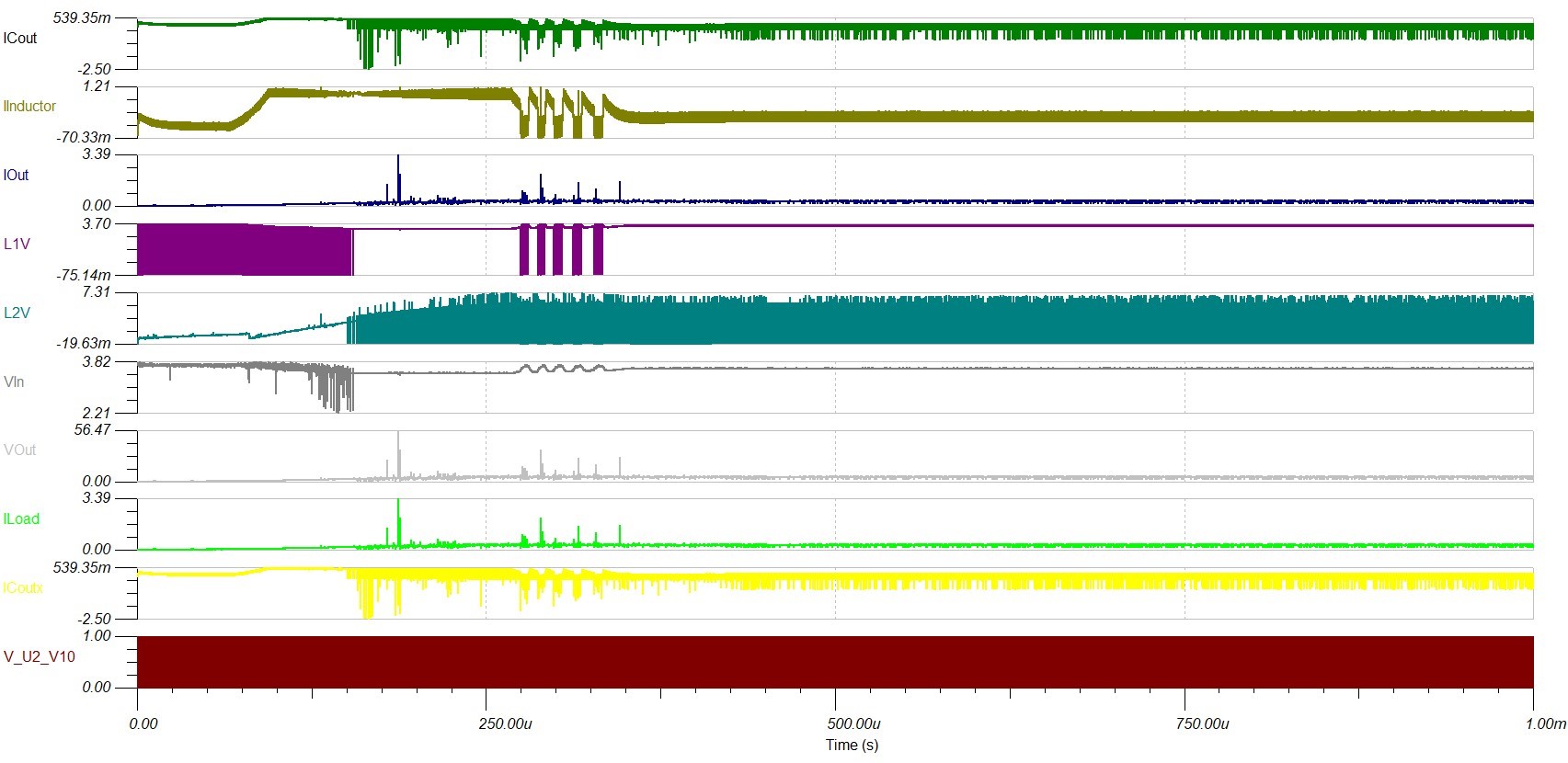

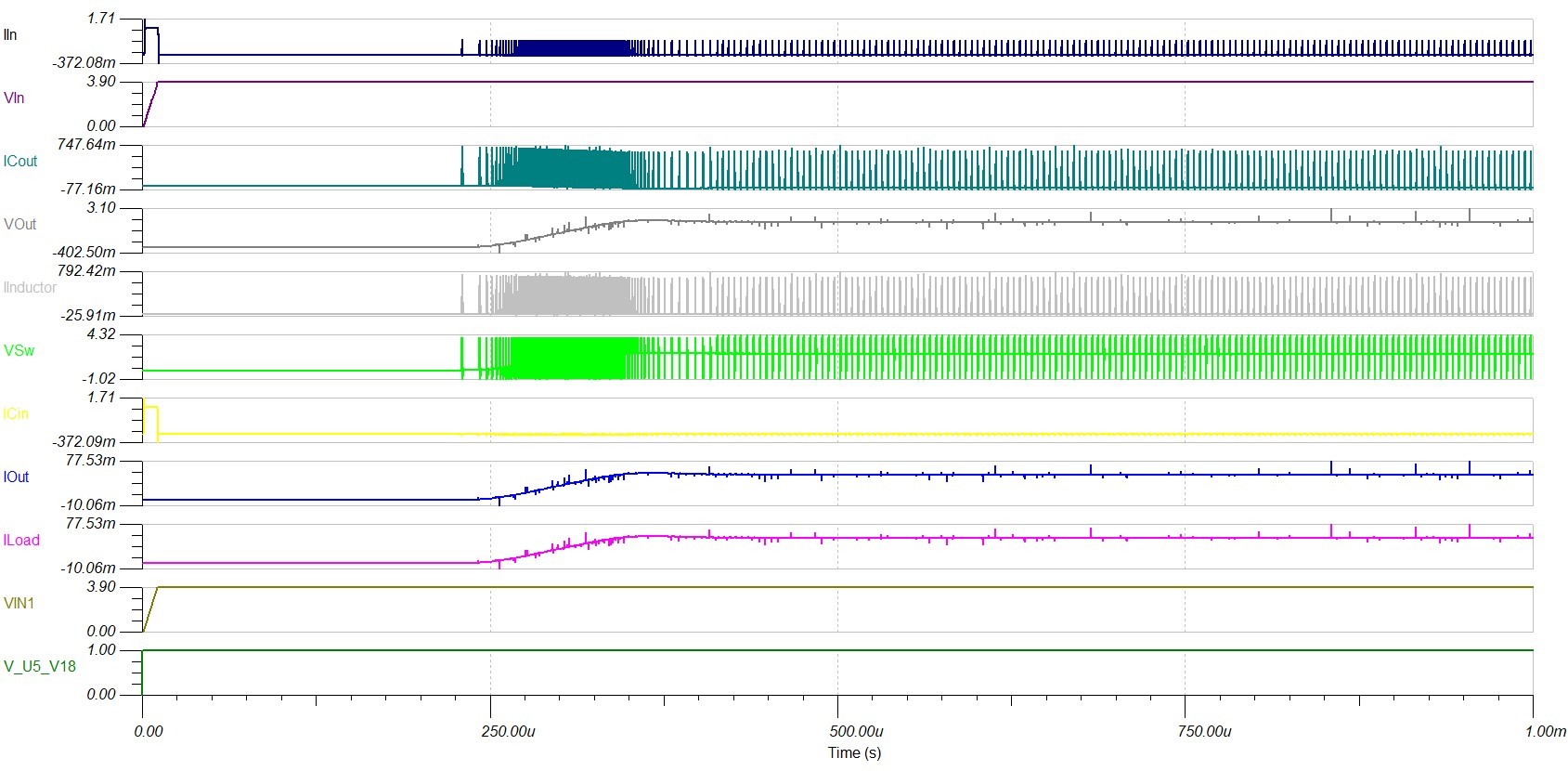

I exported the file and run transient simulation in TINA-TI, and this is the response I received:

Please note the Vout stable at 5V and Iout stable at 300mA.

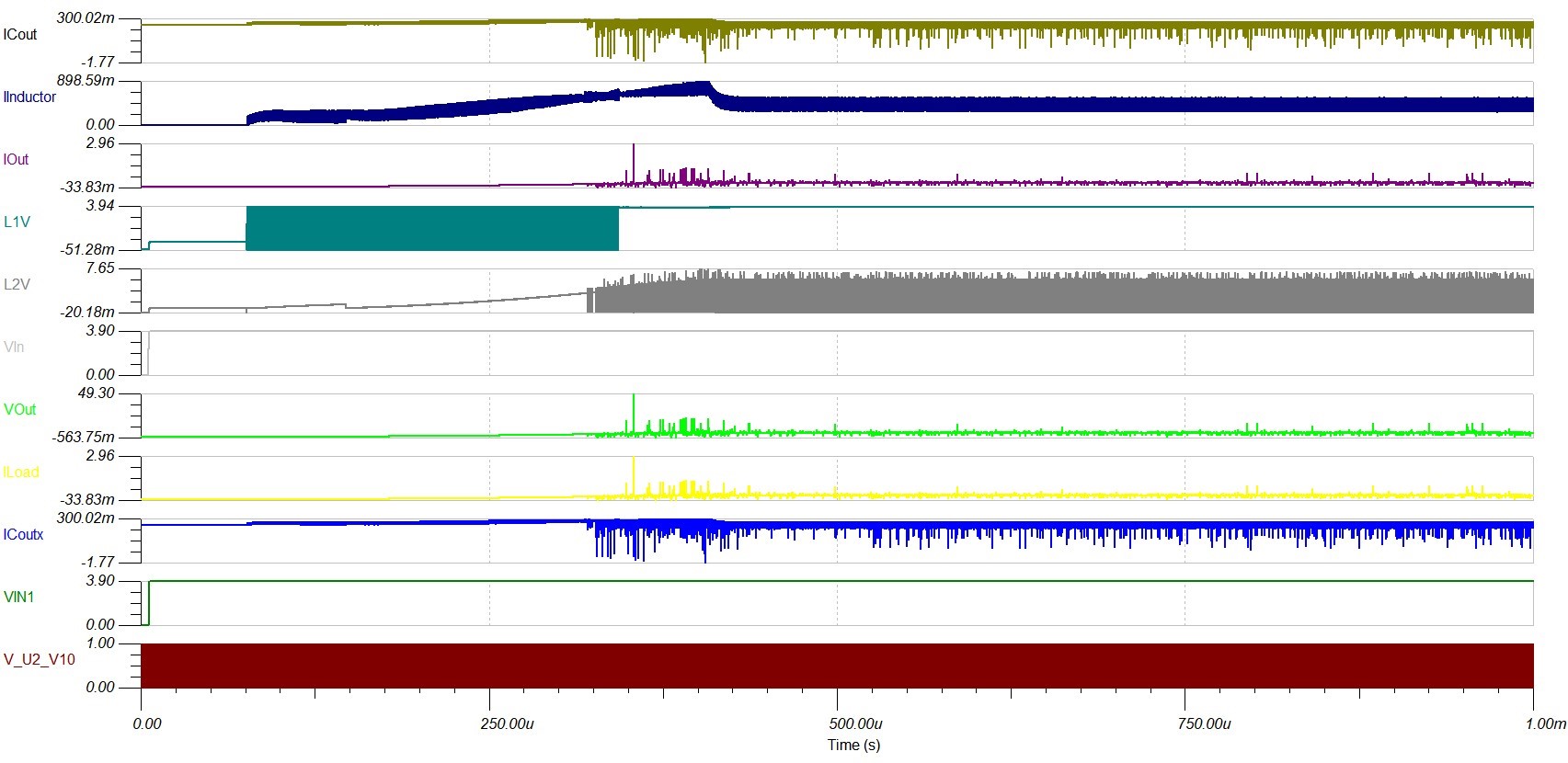

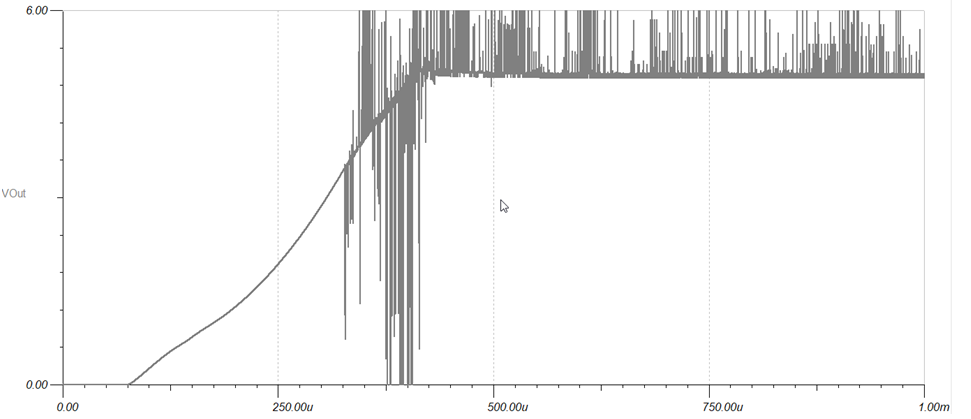

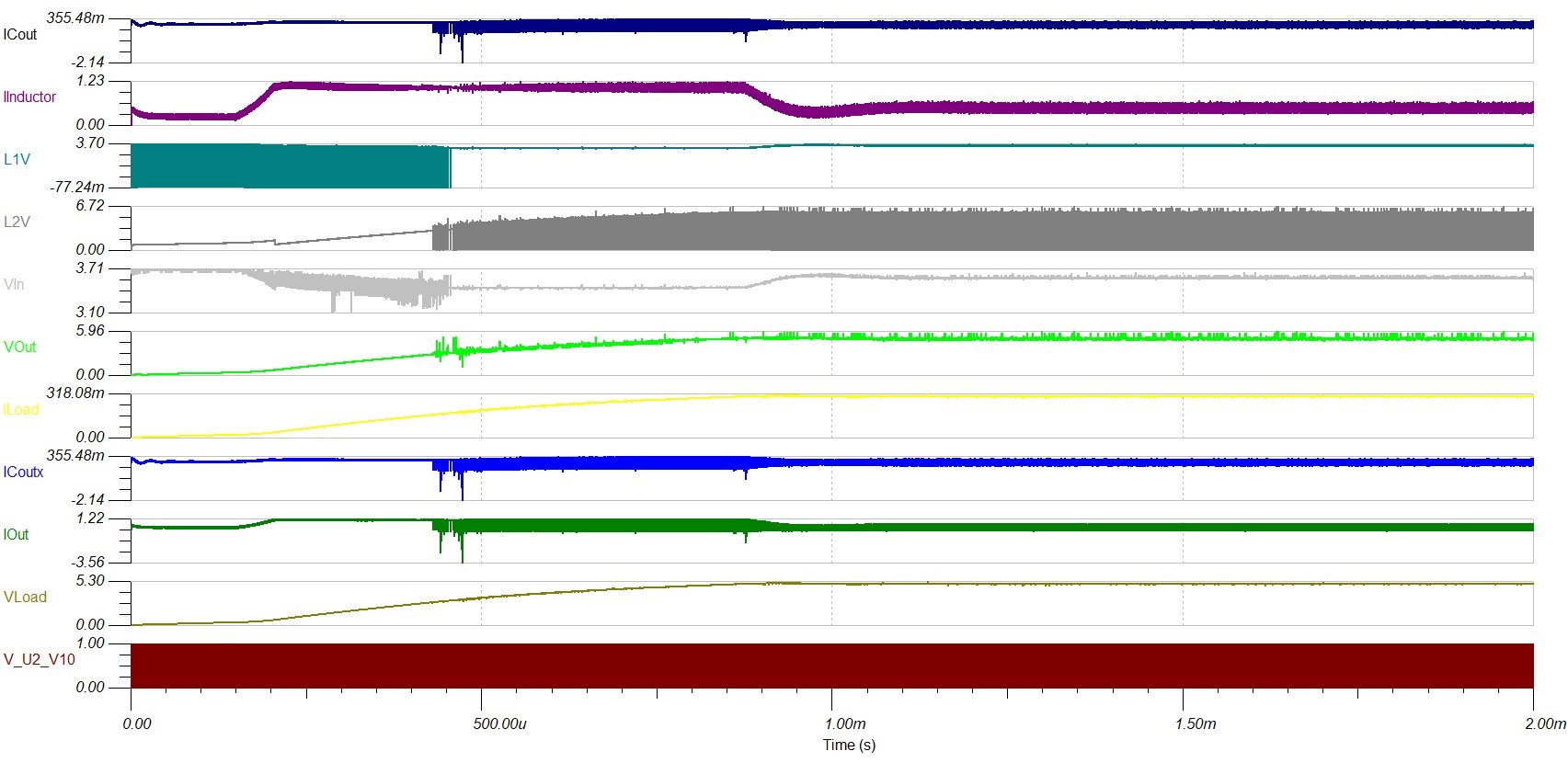

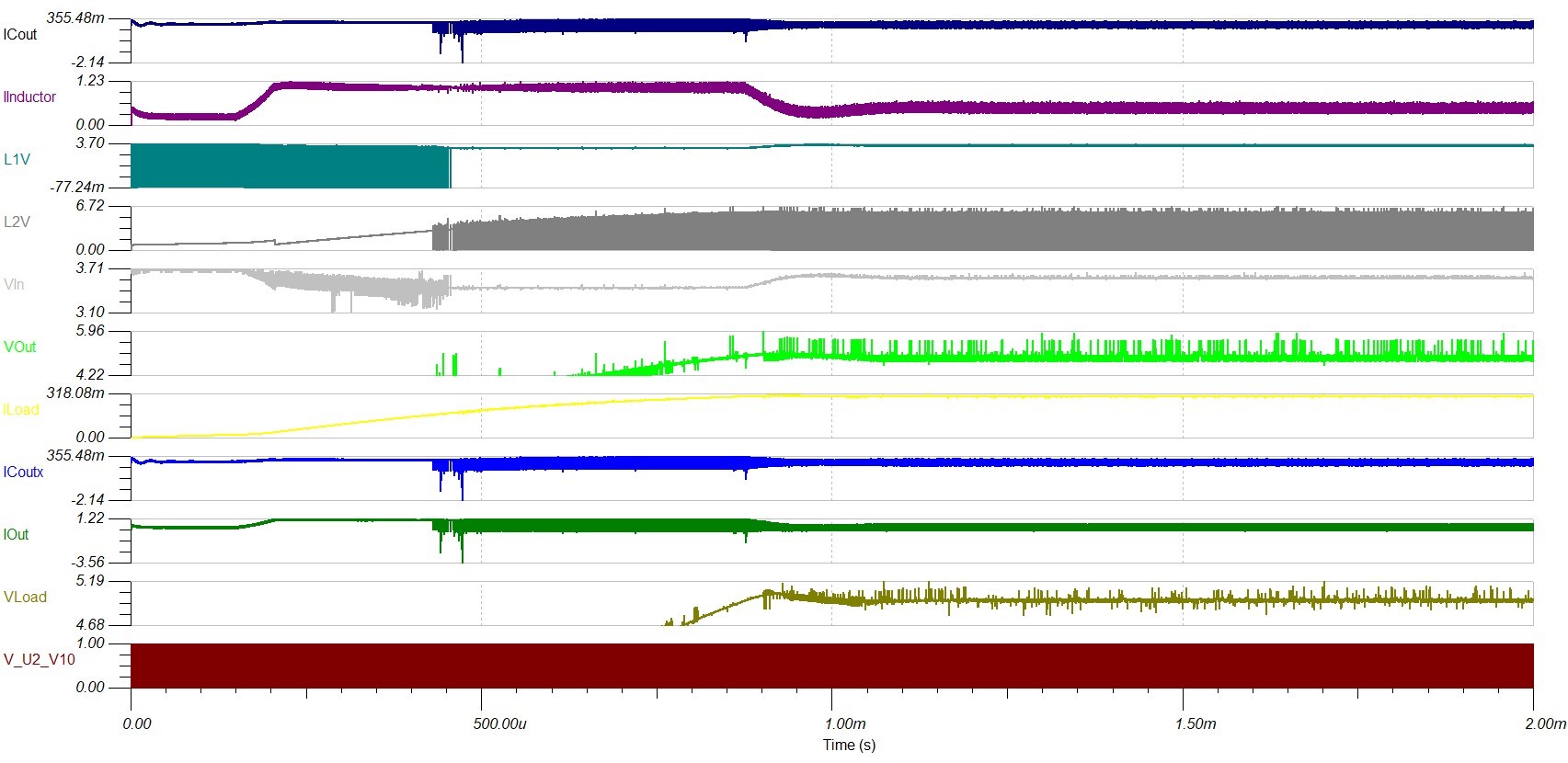

When I started checking the individual components, I found out that the spice file provided by the manufacturer of Cout and Coutx (both are the same in this application, Part No.: EMK107BBJ106MA-T, Manufacturer: Taiyo Yuden) and the one included in the original file exported from WEBENCH Power Designer were not the same. When I replaced both these capacitors in the original file by the spice macros I downloaded from the original manufacturer, this is what TINA-TI is giving:

Please note the highly unstable nature of all the node voltages and currents.

It seems the system went into instability!

This has created an ambiguity capable enough to shake my trusts in WEBENCH tools and the content they provide!

Could anyone please from the TI family please come forward to help me understand how there exists such a big difference in the design files of the same device (as small as a capacitor) provided by the original manufacturer and provided by the WEBENCH tools.

Also, it would be really helpful if anyone could guide me towards how to bring the system back into stability.

Please find both the simulation files attached herewith.

Looking forward to hearing back soon.

Warm regards,

Abbas Mehdi.