Other Parts Discussed in Thread: LMK04828, , ADC12DJ3200EVM, LMX2594, TIDA-01021

Hello,

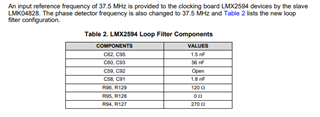

I am following "TI Designs: TIDA-01023 High-Channel-Count JESD204B Clock Generation Reference Design for RADAR and 5G Wireless Testers" to clock my ADC12DJ3200EVM boards. The document instructs to load "1023_LMK04828EVM_Master_3GREF_300MOut_37.5MSync_Output_Distribution.tcs" in TICSPro to program the LMK04828 in distribution mode. I would like this file modified to use a 2 GHz reference and also allow for a third slave clocking board on DCLKout4 and SDCLKout5.

Additionally, the document instructs to load "1023_BRDx_LMK04828_300MREF_300MFCLK_37.5MSYSREF.cfg" in the HSDC TID GUI. I already have firmware for my clocking boards that is working with my ADC12DJ3200EVM boards, so I would like the attached firmware modified to work with the LMK04828 reference source, keeping the output clocks the same if possible so that I can continue to use the same firmware for the LMX2594 and my ADC12DJ3200EVM boards. I have attached the LMX2594 firmware that I am currently using as well.

Thank you,

Alex