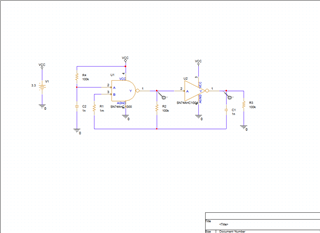

Other Parts Discussed in Thread: SN74AHC1G00, SN74AHC1G04

Dear,

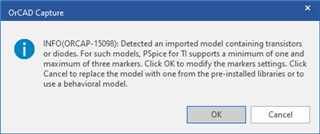

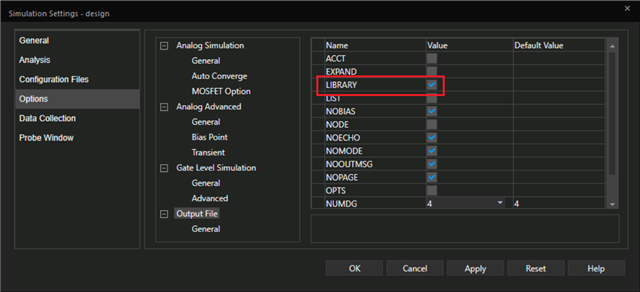

I received an error infor shown as below.

ERROR(ORPSIM-16583): Detected an imported model containing transistors or diodes. For such models, PSpice for TI supports a minimum of one and maximum of three traces. Reduce the number of traces and simulate again.

How should it be solved?