Other Parts Discussed in Thread: CSD19537Q3

Hi Guys,

Good day.

Could you help us to check our customer's design. We have attached here an schematic for your review.

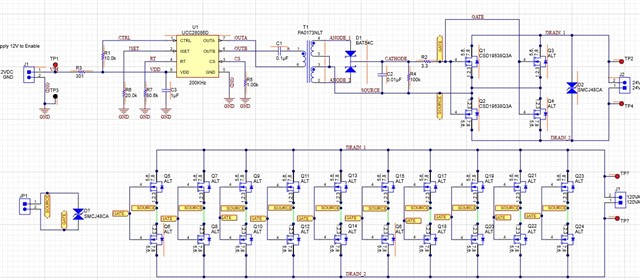

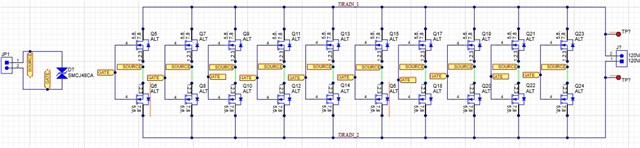

Our customer customized the board by designing a new PCB board where instead of just adding only Q3 and Q4 as shown in the original PCB board, they add several FETs and connect the Source (PIN 1, 2 and 3) and Gate (Pin 4) of the N-Channel MOSFETs via the JP1 connector. According to the original design of PMP12072 REV A, you can get more POWER or CURRENT by simply adding more of Q3 and Q4, therefore, they have added more of Q3 and Q4 and placed them onto a different PCB board. That way, it will have a smaller PCB that is easier to cool using a single heat sink.

Q3 to Q24 on the schematic are N-Channel Power MOSFETs CSD19537Q3 (MOSFET MOSFET 100-V, N channel NexFET power MOSFET, single SON 3 mm x 3 mm, 14.5 mOhm 8-VSON-CLIP -55 to 150)

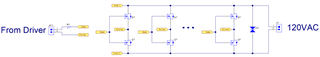

As you can see in picture 2 (let's call it the POWER STAGE), they can make more of the Power Stage PCBs to add either more Current or Power without the need to manufacturing another driver circuit (i.e the primary side with the transformer). Therefore, a single driver PCB board can drive several Power Stage PCBs (in picture 2) by connecting the GATE and the SOURCE of the N-Channel Power MOSFETS via the JP1 connector.

If you think it is not feasible, kindly let us know so our customer can find another way to add more current or Power for their project.

In addition to that. Could you also enlightern us about the frequncy used. is the frequency fixed? If not, how can you control the frequency? Do you think RT controls the output frequency, which means if they use a variable resistor, then they can tune the frequency.

Thank you in advance for the support.

Best regards,

Jonathan