Other Parts Discussed in Thread: LMG5200, BOOSTXL-3PHGANINV

Hello. Help me.

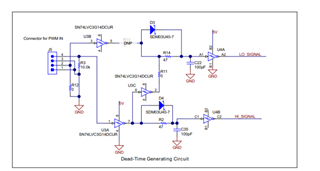

This is a 100V schematic of the LMG5200 of the BOOSTXL-3PHGANINV substrate.

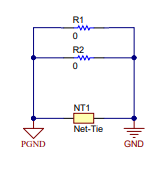

I want to analyze this circuit, but PSPICE has only 80V of LMG5200, so I want to create a circuit as shown in the image above.

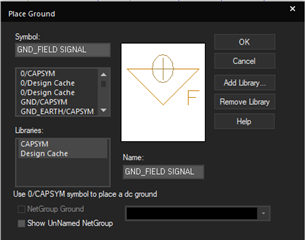

So how do you make PGND in the red frame of the image on PSPICE?

Best regards..

Tosi