Other Parts Discussed in Thread: SFRA

Greetings,

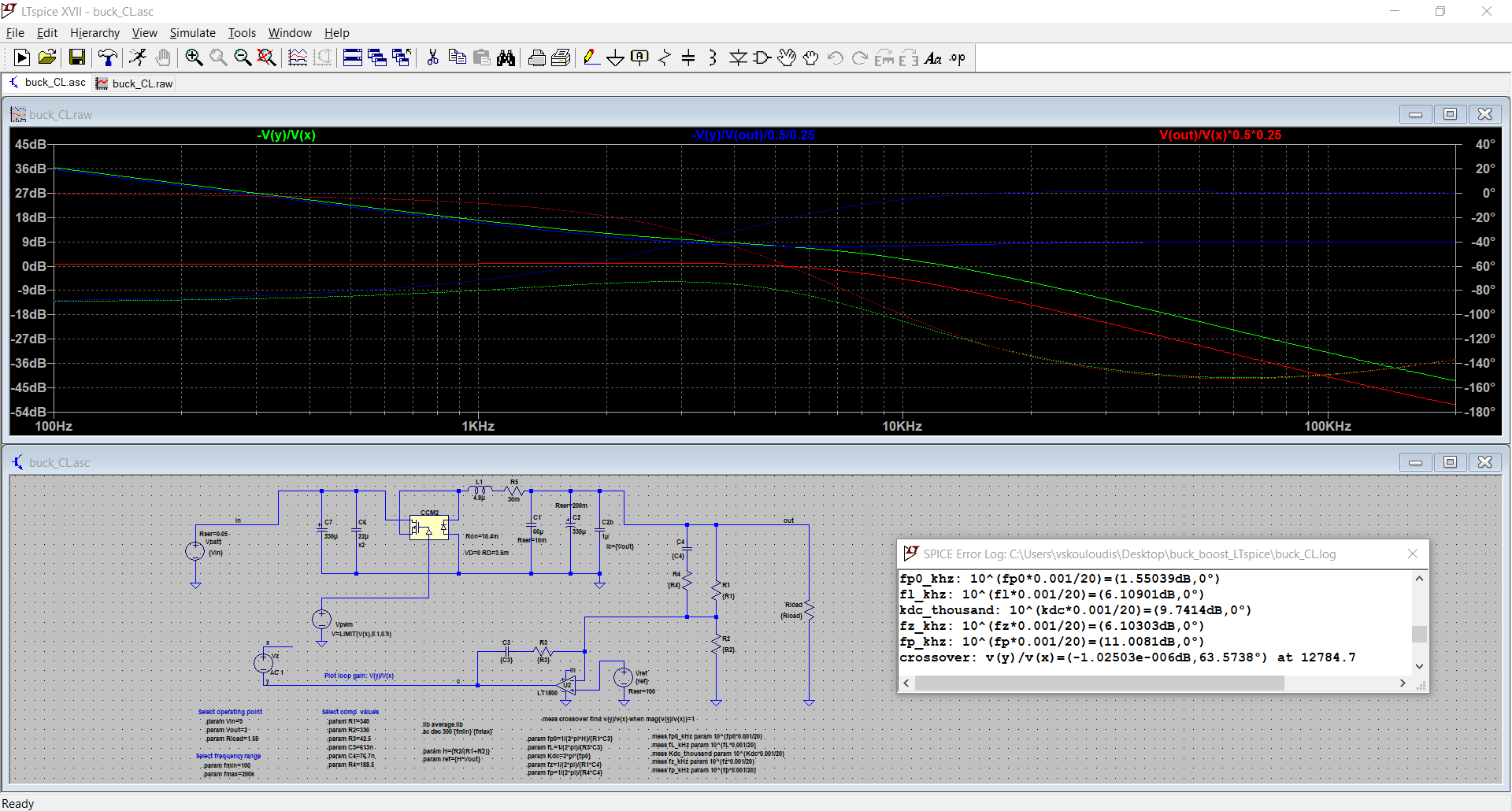

When the Software Frequency Response Analyzer (SFRA) plots the frequency response of the Buck plant (Control-to-Output tranfer function), does it take into account the scaling factors of both the output and input resistive dividers that are used in order to feed the output and input voltage respectively to the ADC pins?

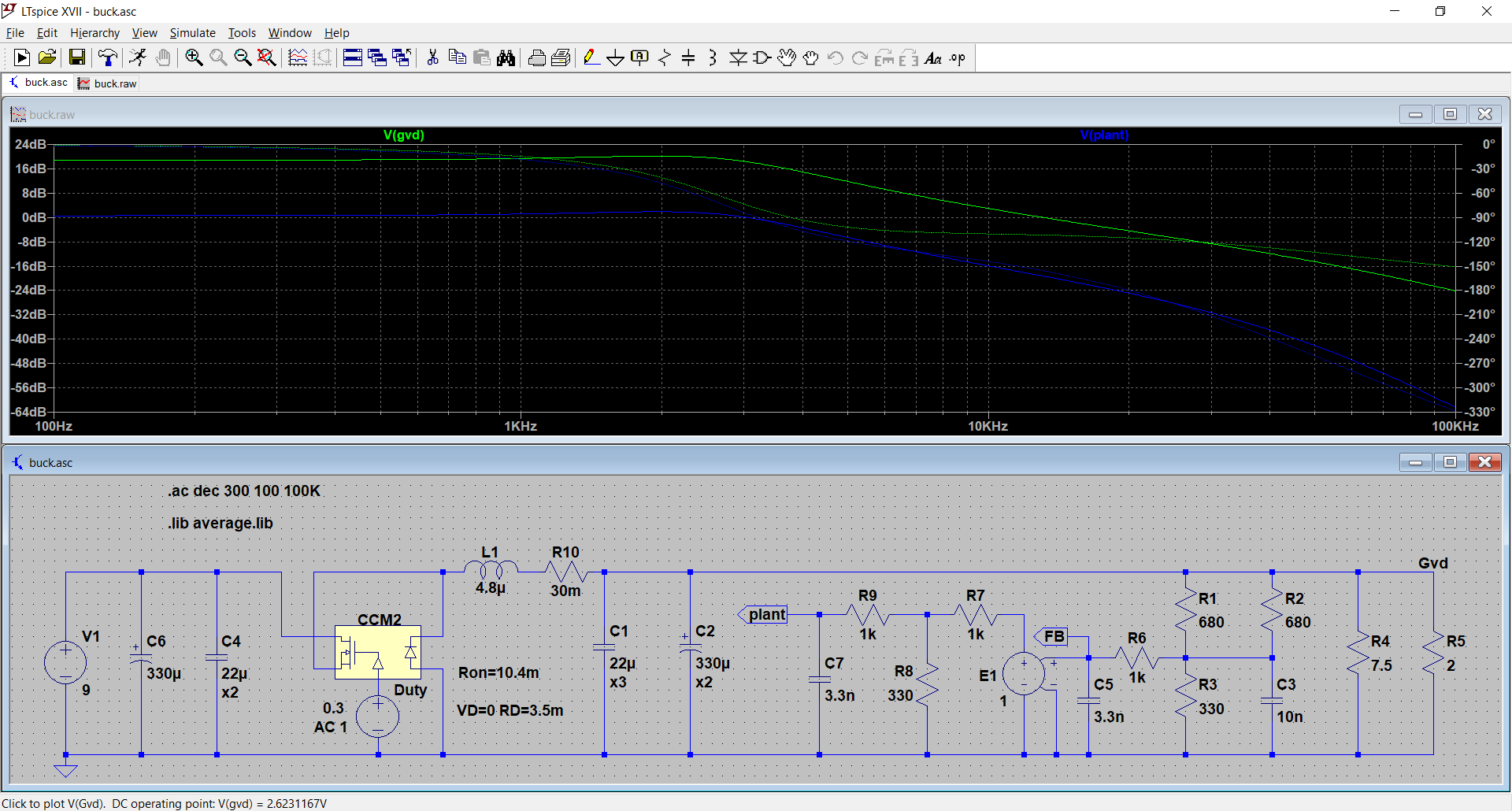

If we did not take any scaling into account, I would expect the plant transfer function of the Buck converter to have a DC gain equal to the input voltage, namely 9V or 19 dB. However, the plot shown has a DC gain just above 0dB.

However, If I scale the plot by multiplying with both the divider ratios, namely [330R, 1K] on the input and [330R, 340R] on the output, then I do get close to the DC gain shown.

Could someone please clarify how the plant function is actually constructed?

Thank you very much.

Kind regards,

Vyron