Other Parts Discussed in Thread: LPV802

Hello.

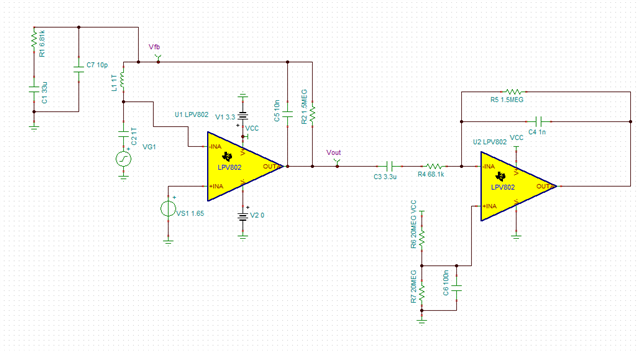

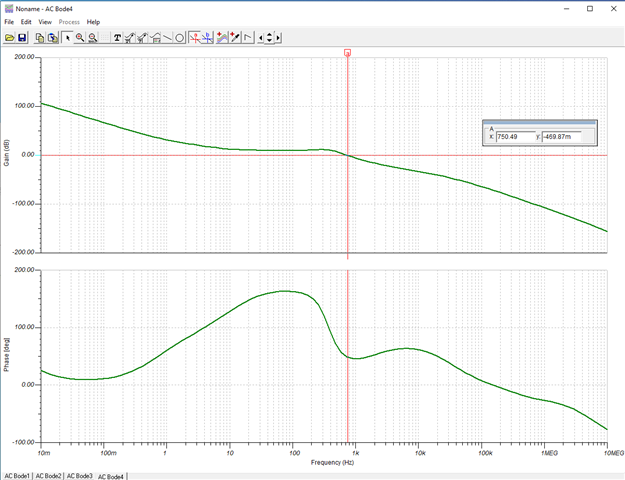

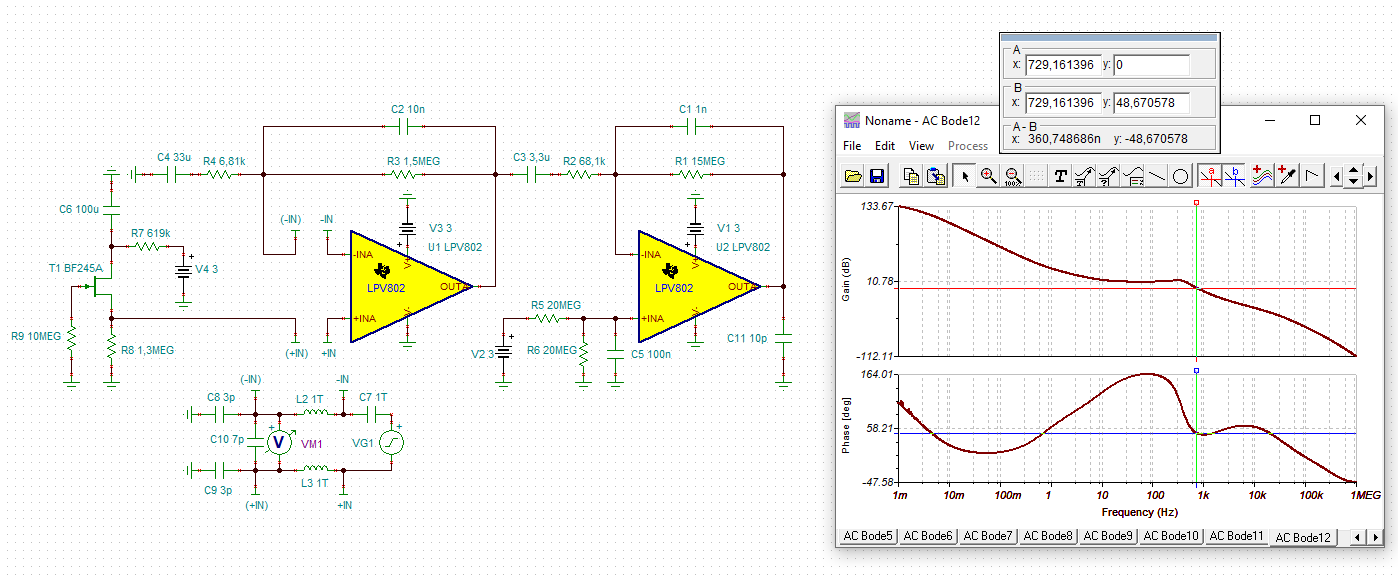

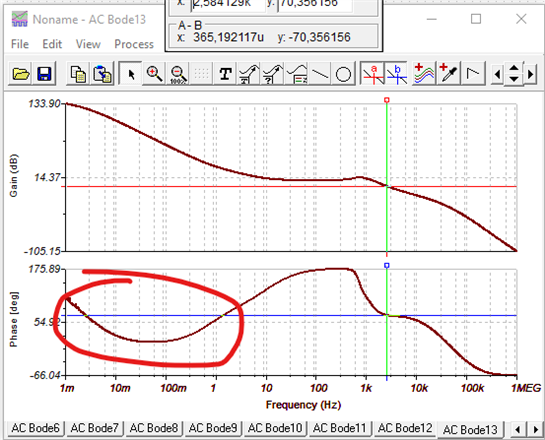

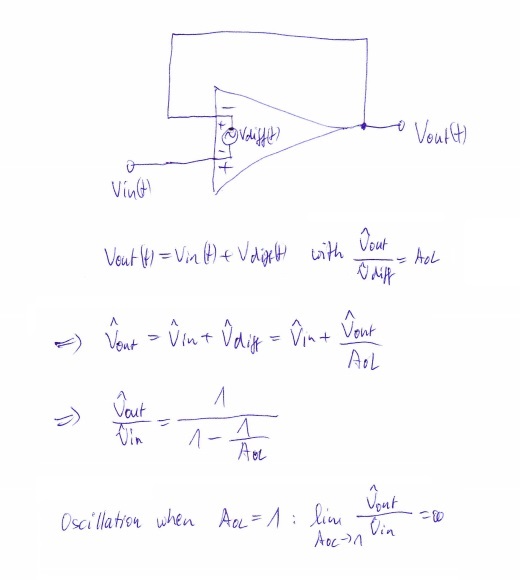

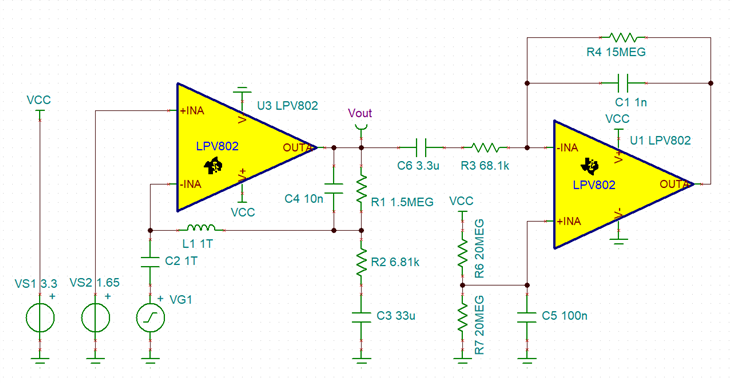

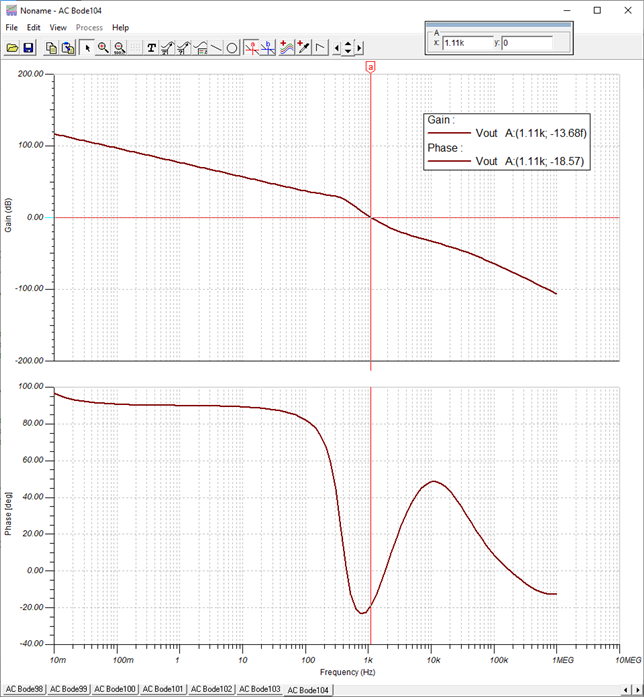

I'm attempting to measure the phase margin of a TI reference design (TIDA-00489) using the method outlined in https://training.ti.com/ti-precision-labs-op-amps-stability-spice-simulation?context=1139747-1139745-14685-1138805-13850. According to this simulation, if I'm doing it correctly, the first gain stage of the amplifier chain appears to be unstable. I can't imagine this to be the case with a reference design, so I must assume I am performing the analysis incorrectly. Can someone validate or correct my method?

Thanks.