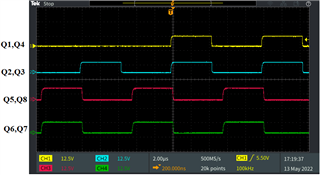

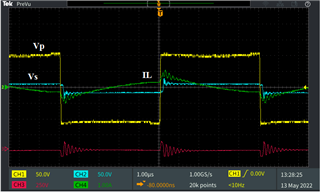

We are trying to transfer power from the primary to secondary side of the DAB converter. Accordingly, all the switches are operated at 50% duty ratio and appropriate deadband has been introduced between the complementary switches of each leg. Also, we have provided phase shift to the gate pulses of the secondary side switches keeping the primary side as the reference. However, the obtained waveforms of inductor current seems to be similar to the ones as shown in Fig. (4.42), page 77 in TI's reference design TIDA-010054. The diagram explains how inductor current should behave during reverse power flow but we are getting similar waveforms during forward power flow. The MOSFETS and the DC-bus capacitors at the secondary side are also getting heated up. To debug this problem, we checked the switching pattern of both the sides of the DAB converter at startup. The switching patterns including the other waveforms are attached herewith for your reference. Please have a look at our results and let us know if we are doing anything incorrectly.

Figure. 1: Switching pattern of both primary and secondary side switches during startup without phase shift

Figure. 2: Primary and Secondary transformer voltages with phase shift and inductor current

Figure. 3: Gate pulses of Q1 and Q5 with phase shift, Primary transformer voltage and secondary side output capacitor current ripple