Part Number: TIDA-020031

Hi,

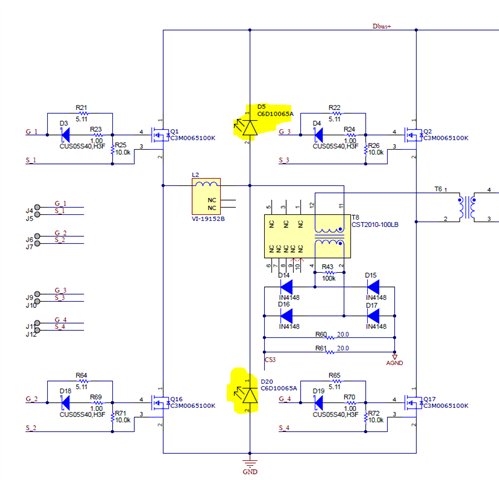

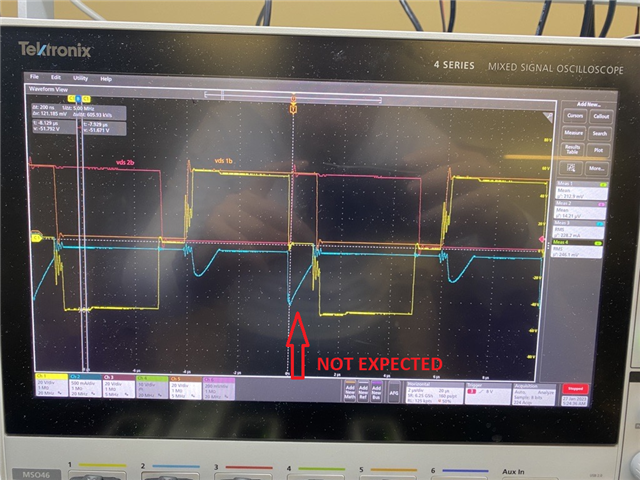

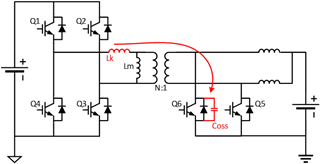

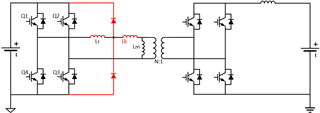

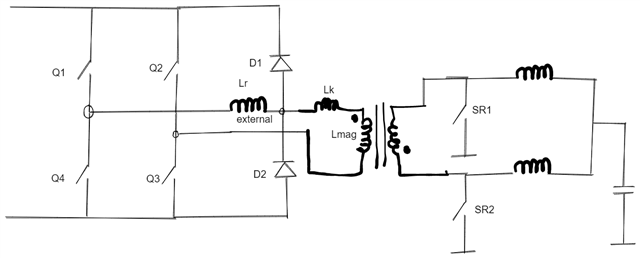

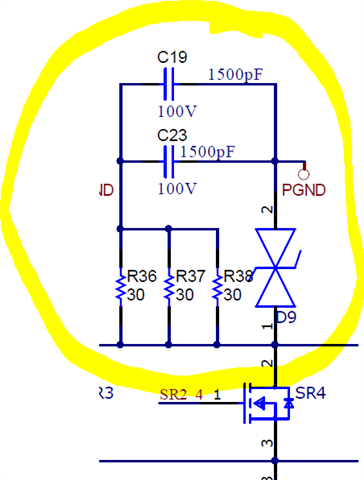

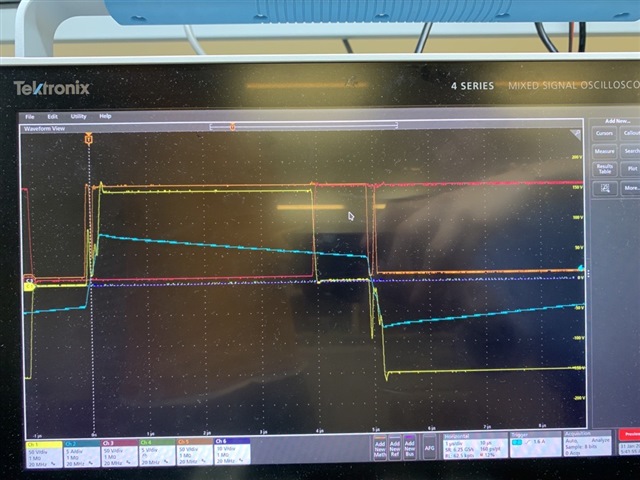

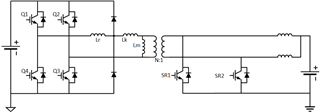

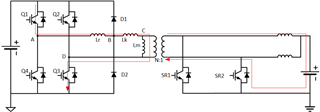

I'm investigating the power stage schematic files of TIDA-020031, which is phase shifted full bridge converter. I'm trying to understand the purpose of schottky diodes mounted as below.

1) Could you please comment on what the purpose is putting such diodes at that node?

2) What is the advantage and disadvantage of putting those diodes?

3) Does D5 prevent charging of Coss of Q17 and discharging of Q2 after turning OFF Q17?