Other Parts Discussed in Thread: CSD19535KTT, CSD19535

The 1kW bldc controller (TIDA-00281) Reference Design provides excellent information for beginners and experts. Which will be more useful for those who eager to know about controllers.

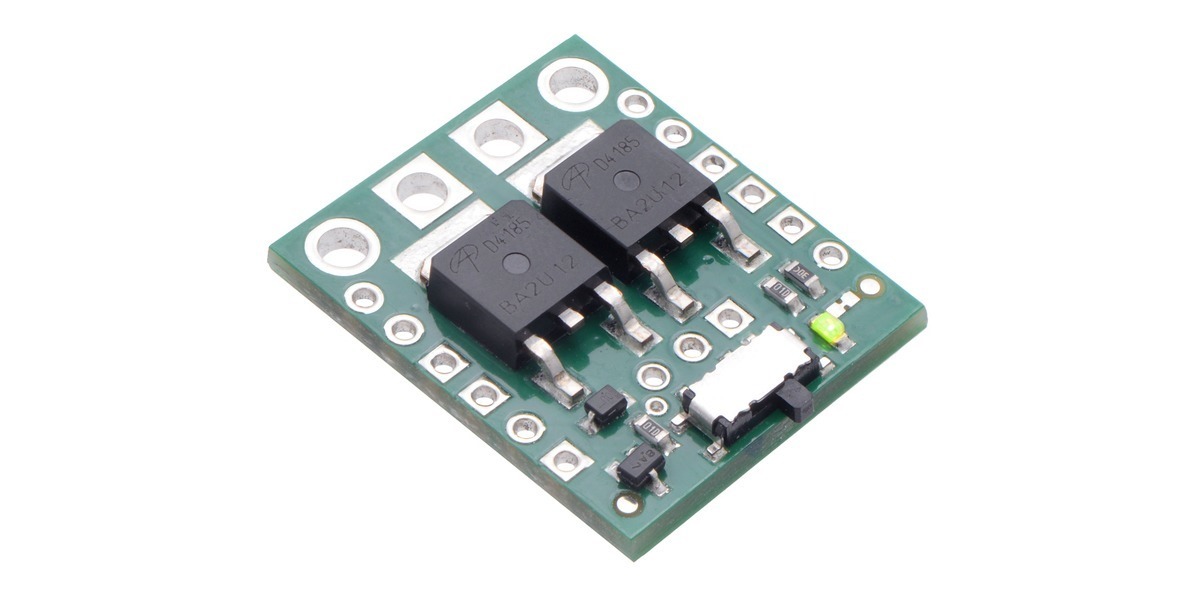

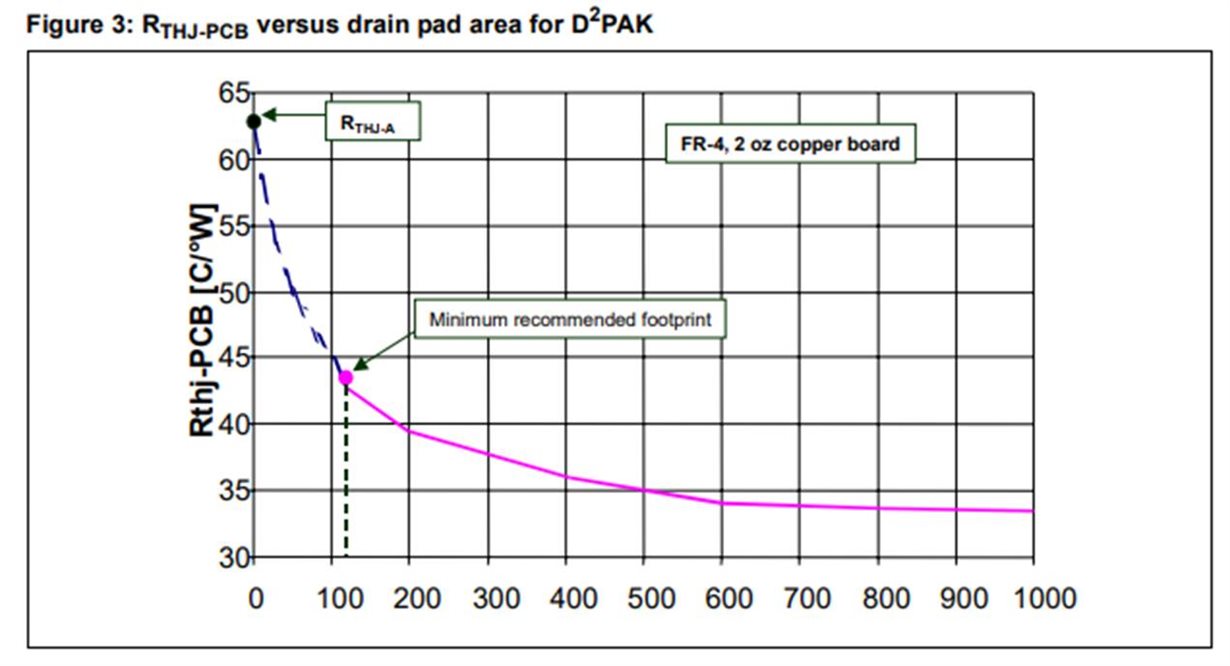

Sir have a doubt , the mosfet that mounded on the PCB (heat sink attached in the PCB). The mosfet's drain is on the backside of fet, so its necessary that individual heat sink should be needed for fets. So in TIDA-00281 design (like the below image) the heat sink is mounded on PCB, is that enough for 1Kw controller. Can you send some reference design of back side of PCB. (The heat sink design)