Other Parts Discussed in Thread: TINA-TI

Tool/software: TINA-TI or Spice Models

Hi,

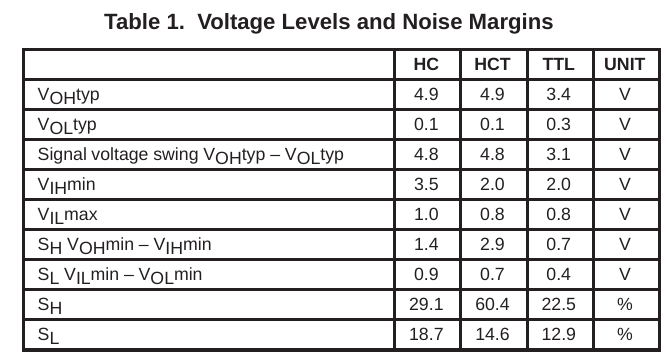

I noticed that when using the TINA-TI HC series models the input on all the family devices do not show any significant hysteresis. According to the data sheets the HIGH level should be ~ 30% below VCC and LOW should be ~30% above GND.

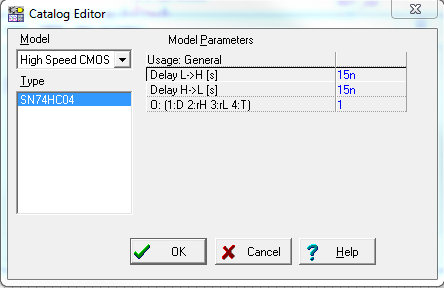

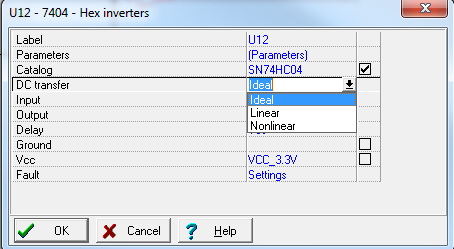

The attached .TSC shows 3 simple gates demonstrating switching with just 33.4mV delta on the inputs, around the transition point. This makes the models unrealistic, particularly where RC timing circuits are employed. Even by selecting Linear or Non-Linear transfer characteristics they do not seem to observe the HC family definitions.

I recognise that the values in the table above are defined at 5V Vcc, however the models seem to offer a very very small noise margin way less than what is expected.

Do I have outdated models, or am I mistaken?

All the best

Aidan