Hi,

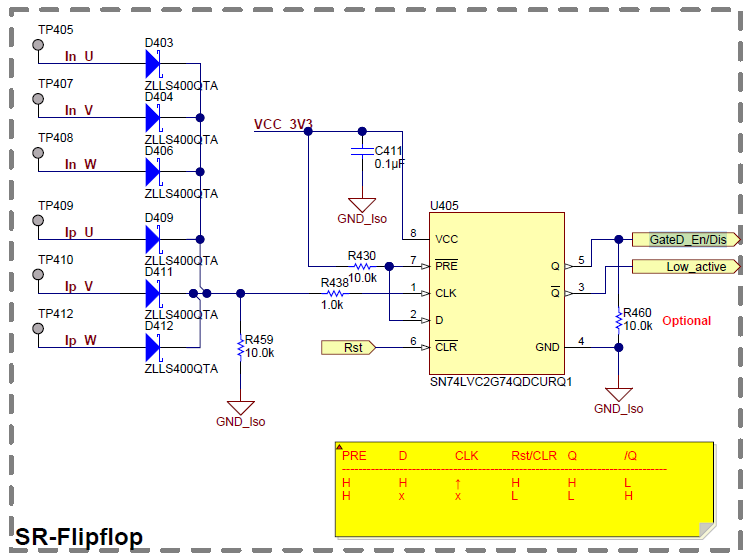

I have confusion or need clarification regarding the protection circuit that is given in the TIDA-01418 Automotive high voltage, high power motor driver reference design for HVAC compressor reference design. The SR flipflop is used to latch the fault and disable the Gate.

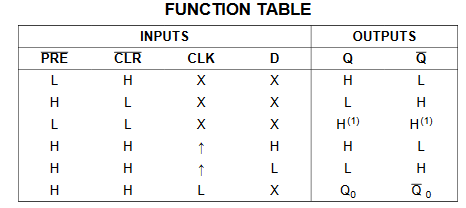

Here, my question is when there is a fault (CLK=H) and the user pressed reset Rst (CLR'=L) then the output is given low (Q=L; enable gate). The output should be high (Q=H; disable gate) if CLK = H i.e. during fault irrespective of other input states.