Other Parts Discussed in Thread: UCC21732-Q1

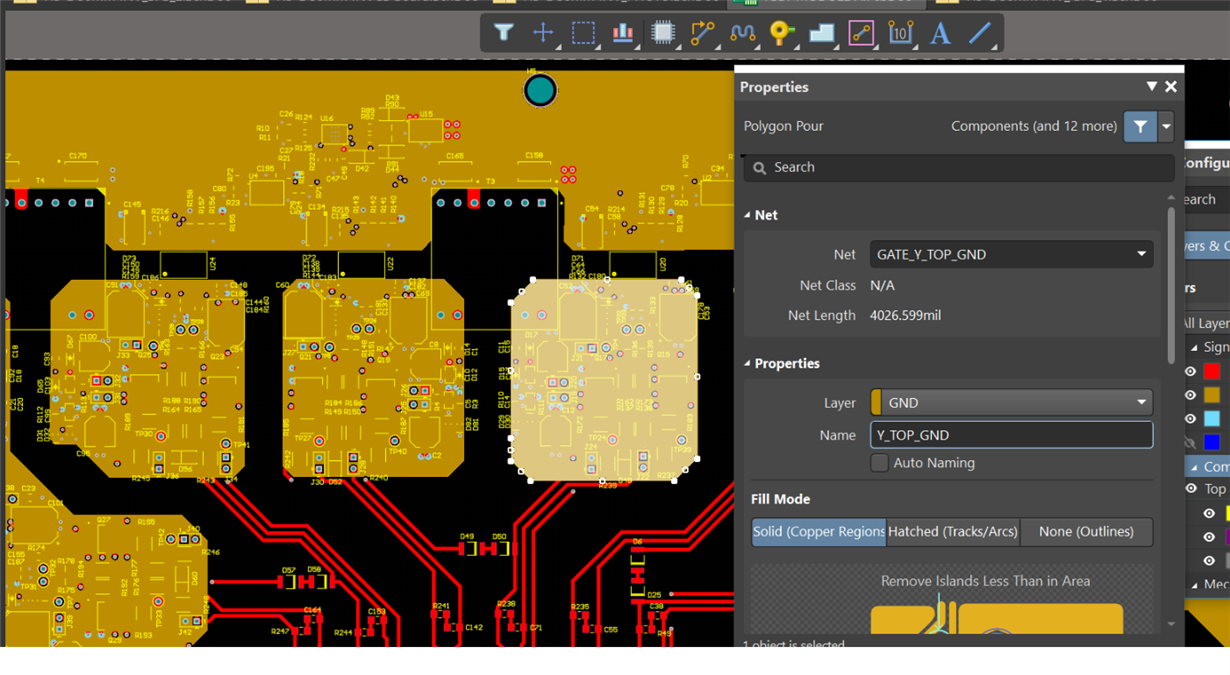

We found layout problem on the TIDA-00195.

In the layout, it places a ground plan which is connected to GND2 for sensitive signal layer on high side IGBT gate driver.

My question is the GND2 for the High side gate driver is coming with high dV/dt. the device and around IC could be influenced by the dV/dt, correct?

On the layout guide of the UCC21732-Q1, it mentions it's only for the low side gate driver, not recommend for high side gate driver.