Other Parts Discussed in Thread: DRV8323

Hi,

I am interested in the portion of the TIDA-00774 which relates to the single Low-Side Current Sense Amplifier. I understand that in this this Reference Design, R17 and R18 are not populated and the CSA is disabled.

However, I have a few questions which I hope you can answer.

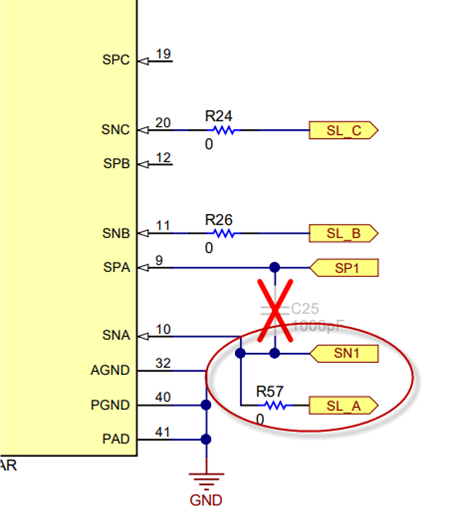

Question #1 - The Current Sense Amplifiers for Phases B and C are not used. The datasheet indicates "If any of the three current sense amplifiers are not being used, they can be tied off by shorting the

SNx pin to the SPx pin and leaving the SOx pin unconnected". Why are the SPC-SNC and SPB-SNB not shorted together? Is there a technical advantage to leaving these inputs open?

Question #2 - The SNA input is tied to both SL_A and SN1. SN1 is connected to the Battery Ground side of the Sense Resistor while SNx is shown in the Datasheet as connecting to the MOSFET-side of the Sense Resistor. Is there a reason for connecting SNA to SL_A and SN1 instead of connecting SPA to SL_A and SP1?

Thanks,

Tom