Part Number: PMP4259

Dear TI expert,

I designed a 3 KW PFC boost converter according to PMP4259 reference design based on UCC28070 controller. My design components are attached as a PDF file.

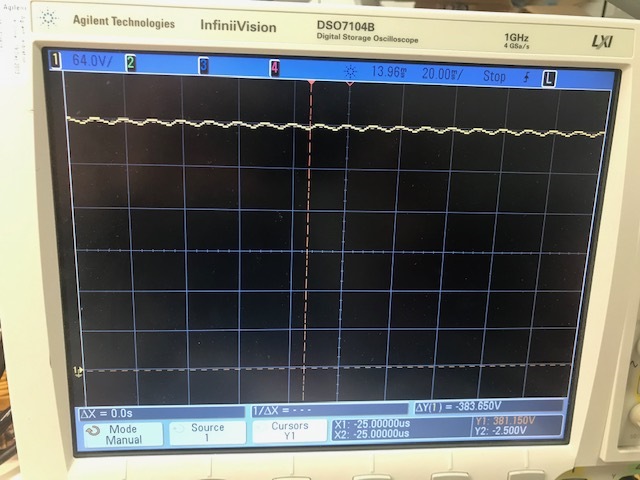

In about 391W output load (383V, 375ohm) all of the required parameters are met as in figures I attached. However, when I connect higher load (600w, 240ohm), the circuit becomes unstable, sinks a lot of current and usually a MOSFET breaks out. I checked all of the gate and CT signals and they seem to be fine. Do you have any idea how I can attack this problem?

By the way, I have removed current sense PWM ramp circuit and add only 120mV offset to current sense signal. UCC28070_PFC _185-265-400.pdf