Hi,

My customer is considering using DP83822 and refers TIDA-00299 schematic.

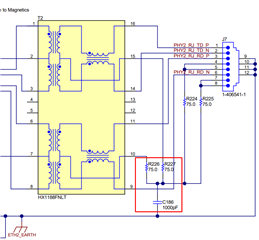

The center tap of the pulse Trans is divided as below on this TIDA;

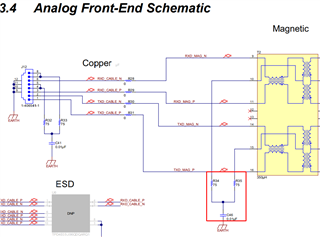

On the other hand, the center tap is connected directly as below on the EVM.

Could you tell me why the center tap is divided on the TIDA schematic?

Best Regards,

Kuramochi