Hi, There,

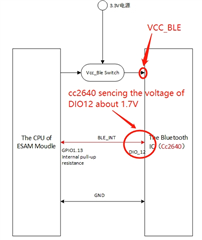

On one of my customer's design, there is 1.7V on the DIO when shut down the VCC. noticed customer, the DIO voltage can't be higher than VDDS +0.3V as description in the datasheet.

there is some functionality problem, e.g. can't bootup normally.

Customer would like to know what the possible reason is and what the risk if they keep current design. hope to get some analysis based on Chip design architecture.

BR. Albin