Hi team,

I believe CC2650 has two resets condition, RESET_N and power on reset (POR) due to VDDS drop.

Could you share reset threshold voltage for each?

Best regards,

Kurumi

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi team,

I believe CC2650 has two resets condition, RESET_N and power on reset (POR) due to VDDS drop.

Could you share reset threshold voltage for each?

Best regards,

Kurumi

Hi,

For reset conditions you can see the register RESETCTL in the TRM.

If a low duration of 1us is detected on RESET_N line, the device will reset.

For POR I will check the exact threshold and let you know.

This thread should also help as general information :

regards

Hi,

Thank you for the reply.

If a low duration of 1us is detected on RESET_N line, the device will reset.

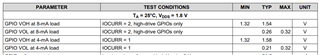

-> So, when we want to force the device to enter reset condition by applying external voltage on RESET_N pin, what is the max voltage we can use? Is it the same with GPIO VOL?

Best regards,

Kurumi

Hi,

The reset pin follows the same voltage levels as other IO pins. You should remain with the VDDS specs for other IO pins.

regards

Hi,

OK, so for example when VDDS=1.8V, then the RESET_N threshold is 0.26V typ for 8mA load. Is my understanding correct?

Also, what is the VDD Power-on-Reset threshold?

Hi,

Your understating is correct. When operating at 1.8V, make sure the supply is stable since there is very little headroom between BOD and 1.8V.

As for POR threshold, I was not able to find exact threshold. However, when the supply is ramping down you will hit BOD first so POR will not matter.

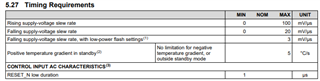

When the device supply is ramping up you need to be within the slew rate requirement as stated in table

regards